4 rx_aack_noclk - rx_aack_on without clkm – Rainbow Electronics AT86RF231 User Manual

Page 60

60

8111A–AVR–05/08

AT86RF231

Short Acknowledgment Frame (ACK) Start Timing

Register bit AACK_ACK_TIME (register 0x17, XAH_CTRL_1), see

defines the symbol time between frame reception and transmission of an acknowledgment

frame.

Note that this feature can be used in all scenarios, independent of other configurations. How-

ever, shorter acknowledgment timing is especially useful when using High Data Rate Modes to

increase battery lifetime and to improve the overall data throughput; refer to

7.2.3.4

RX_AACK_NOCLK - RX_AACK_ON without CLKM

If the AT86RF231 is listening for an incoming frame and the microcontroller is not running an

application, the microcontroller can be powered down to decrease the total system power con-

sumption. This special power-down scenario for systems running in clock synchronous mode

(see

Section 6. “Microcontroller Interface” on page 16

) is supported by the AT86RF231 using the

state RX_AACK_ON_NOCLK. The radio transceiver functionality in this state is based on that in

state RX_AACK_ON with pin 17 (CLKM) disabled.

The RX_AACK_NOCLK state is entered from RX_AACK_ON by a rising edge at pin 11

(SLP_TR). The return to RX_AACK_ON state results either from a successful frame reception or

a falling edge on pin SLP_TR.

The CLKM pin is disabled 35 clock cycles after the rising edge at SLP_TR pin. This allows the

microcontroller to complete its power-down sequence. This is not valid for clock rates 250 kHz

and 62.5 kHz, where the main clock at pin 17 (CLKM) is switched off immediately.

In case of the reception of a valid frame, IRQ_3 (TRX_END) is issued and pin 17 (CLKM) is

turned on. A timing diagram is shown in

. A received frame is considered

valid if it passes address filtering and has a correct FCS. If an ACK was requested the radio

transceiver enters BUSY_RX_AACK state and follows the procedure described in

“RX_AACK_ON - Receive with Automatic ACK” on page 51

.

After the transaction has been completed, the radio transceiver reenters the RX_AACK_ON

state.

The radio transceiver reenters the RX_AACK_ON_NOCLK state only, when the next rising edge

at SLP_TR pin occurs.

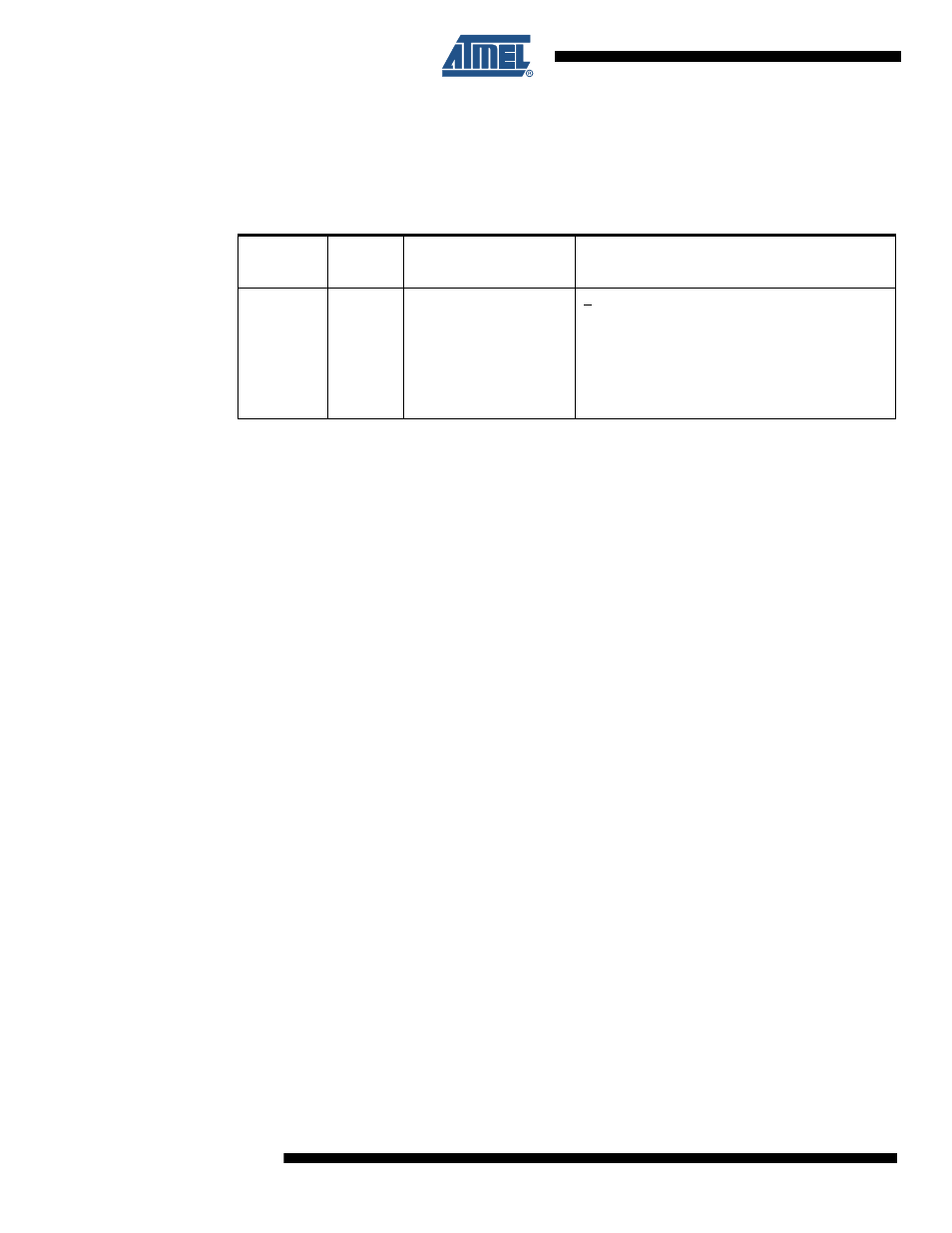

Table 7-11.

Overview of RX_AACK Configuration Bits

Register

Register

Register Name

Description

Address

Bit

0x17

2

AACK_ACK_TIME

0: Standard compliant acknowledgement timing

of 12 symbol periods. In slotted acknowledge-

ment operation mode, the acknowledgment

frame transmission can be triggered 6 symbol

periods after reception of the frame earliest.

1: Reduced acknowledgment timing of 2 symbol

periods (32 µs).