8 dynamic frame buffer protection, 1 overview, 2 register description – Rainbow Electronics AT86RF231 User Manual

Page 154

154

8111A–AVR–05/08

AT86RF231

11.8

Dynamic Frame Buffer Protection

11.8.1

Overview

The AT86RF231 continues the reception of incoming frames as long as it is in any receive state.

When a frame was successfully received and stored into the Frame Buffer, the following frame

will overwrite the Frame Buffer content again.

To relax the timing requirements for a Frame Buffer read access the Dynamic Frame Buffer Pro-

tection prevents that a new valid frame passes to the Frame Buffer until a Frame Buffer read

access has ended (indicated by /SEL = H, refer to

Section 6.2 “SPI Protocol” on page 19

A received frame is automatically protected against overwriting:

• in Basic Operating Mode, if its FCS is valid

• in Extended Operating Mode, if an IRQ_3 (TRX_END) is generated

The Dynamic Frame Buffer Protection is enabled, if register bit RX_SAFE_MODE (register

0x0C, TRX_CTRL_2) is set and the transceiver state is RX_ON or RX_AACK_ON.

Note that Dynamic Frame Buffer Protection only prevents write accesses from the air interface -

not from the SPI interface. A Frame Buffer or SRAM write access may still modify the Frame

Buffer content.

11.8.2

Register Description

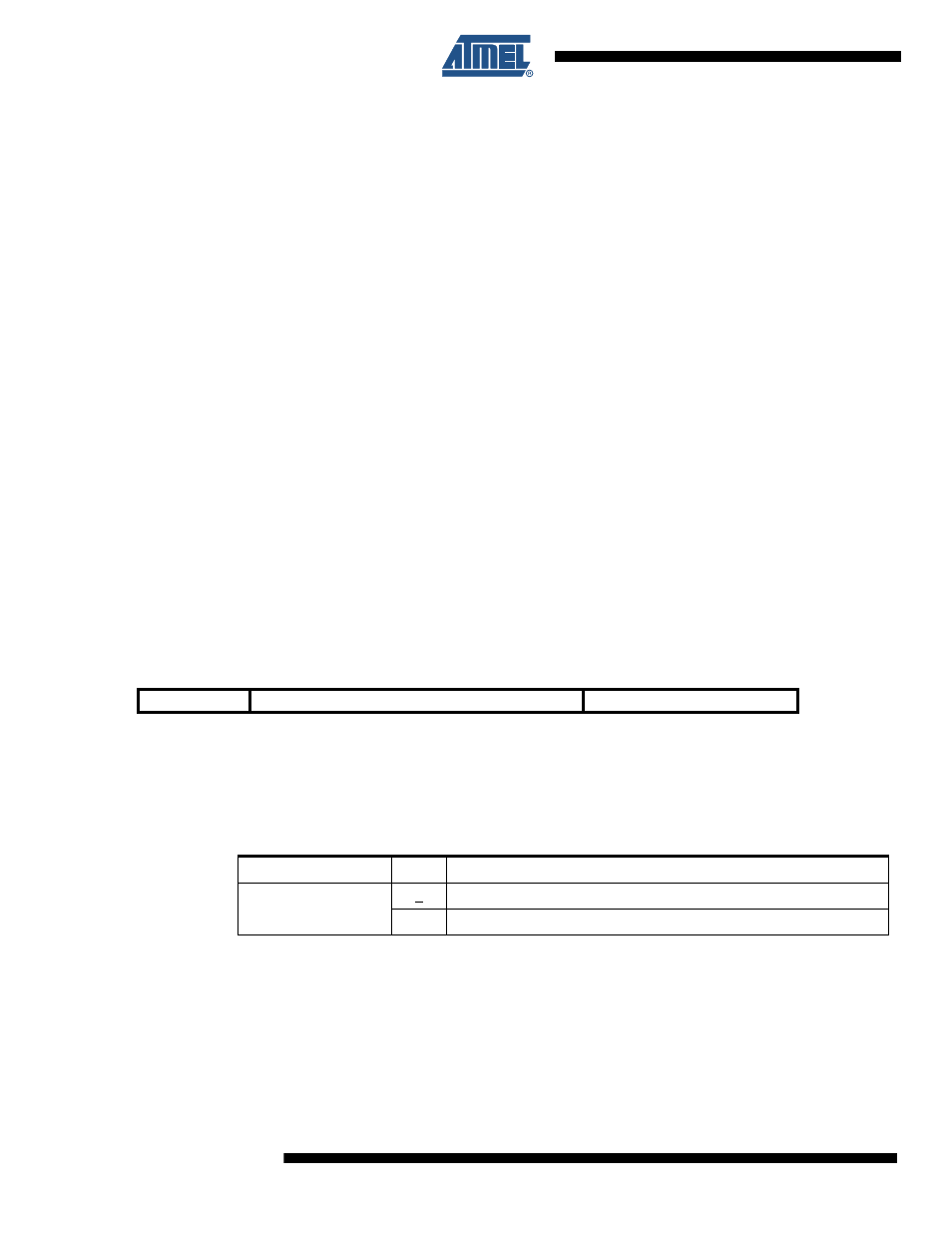

Register 0x0C (TRX_CTRL_2):

The TRX_CTRL_2 register is a multi purpose register to control various settings of the radio

transceiver.

• Bit 7 - RX_SAFE_MODE

If this bit is set Dynamic Frame Buffer Protection is enabled:

Note:

1. Dynamic Frame Buffer Protection is released with the rising edge of pin23 (/SEL) of a Frame

Buffer read access, see

Section 6.2.2 “Frame Buffer Access Mode” on page 20

, or radio trans-

ceiver state changing from RX_ON or RX_AACK_ON to another state.

This operation mode is independent of the setting of register bits RX_PDT_LEVEL, refer to

tion 9.1.3 “Configuration” on page 102

• Bit [6:2] - Reserved

Bit

7

6

5

4

3

2

1

0

+0x0C

RX_SAFE_MODE

Reserved

OQPSK_DATA_RATE

TRX_CTRL_2

Read/Write

R/W

R

R

R

R

R

R/W

R/W

Reset Value

0

0

1

0

0

0

0

0

Table 11-17. Dynamic Frame Buffer Protection Mode

Register Bit

Value

Description

0

Disable Dynamic Frame Buffer Protection

1

Enable Dynamic Frame Buffer Protection