1 description of rx_aack configuration bits – Rainbow Electronics AT86RF231 User Manual

Page 54

54

8111A–AVR–05/08

AT86RF231

7.2.3.1

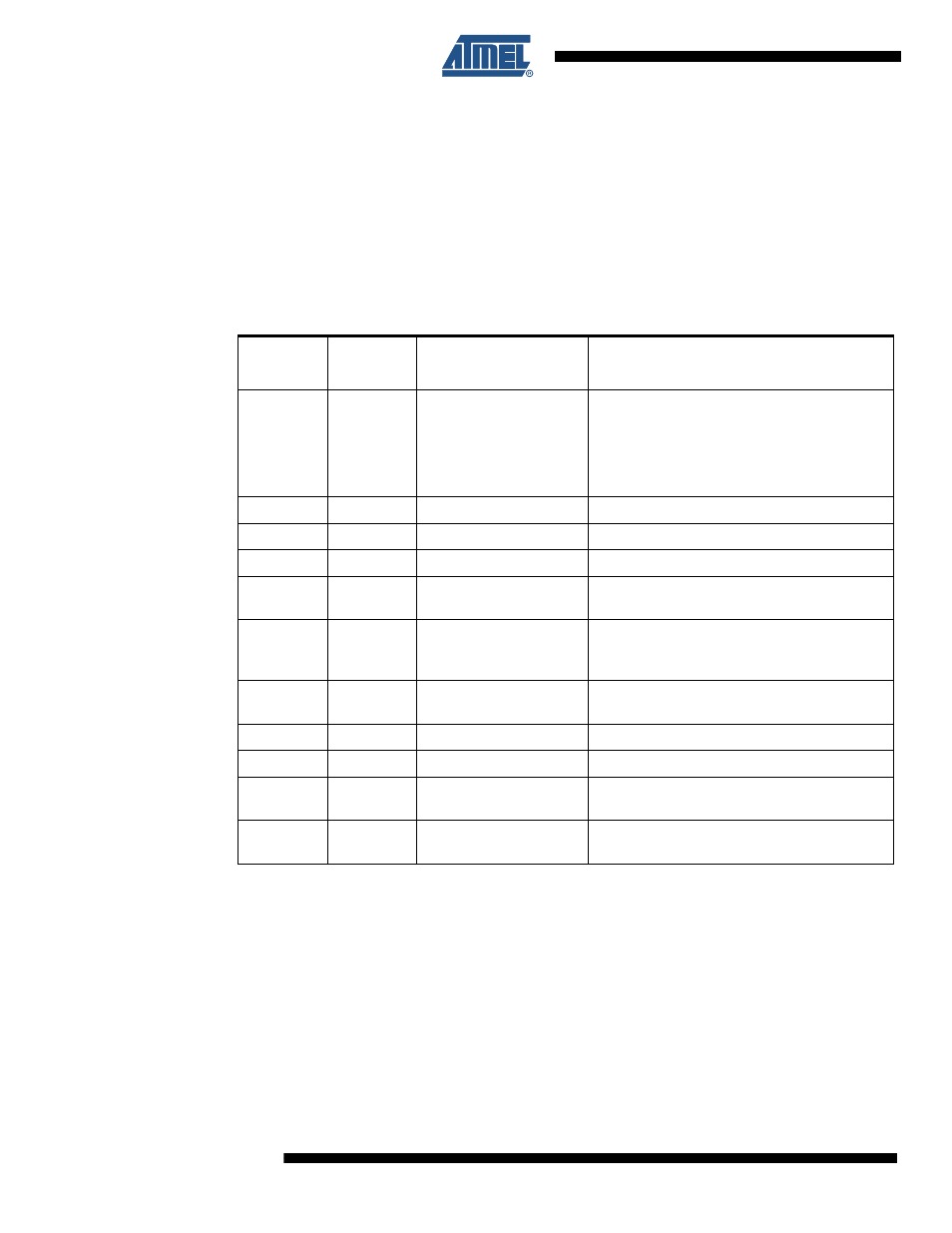

Description of RX_AACK Configuration Bits

Overview

summarizes all register bits which affect the behavior of an RX_AACK

transaction. For address filtering it is further required to setup address registers to match to the

expected address.

Configuration and address bits are to be set in TRX_OFF or PLL_ON state prior to switching to

RX_AACK mode.

A graphical representation of various operating modes is illustrated in

.

The usage of the RX_AACK configuration bits for various operating modes of a node is

explained in the following sections. Configuration bits not mentioned in the following two sec-

tions should be set to their reset values according to

All registers mentioned in

are described in

Note, that the general behavior of the "AT86RF231 Extended Feature Set",

“AT86RF231 Extended Feature Set” on page 128

, settings:

Table 7-5.

Overview of RX_AACK Configuration Bits

Register

Register

Register Name

Description

Address

Bits

0x20,0x21

0x22,0x23

0x24

...........

0x2B

SHORT_ADDR_0/1

PAN_ADDR_0/1

IEEE_ADDR_0

........

IEEE_ADDR_7

Set node addresses

0x0C

7

RX_SAFE_MODE

Protect buffer after frame receive

0x17

1

AACK_PROM_MODE

Support promiscuous mode

0x17

2

AACK_ACK_TIME

Change auto acknowledge start time

0x17

4

AACK_UPLD_RES_FT

Enable reserved frame type reception, needed

to receive non-standard compliant frames

0x17

5

AACK_FLTR_RES_FT

Filter reserved frame types like data frame

type, needed for filtering of non-standard

compliant frames

0x2C

0

SLOTTED_OPERATION

If set, acknowledgment transmission has to be

triggered by pin 11 (SLP_TR)

0x2E

3

AACK_I_AM_COORD

If set, the device is a PAN coordinator

0x2E

4

AACK_DIS_ACK

Disable generation of acknowledgment

0x2E

5

AACK_SET_PD

Set frame pending subfield in Frame Control

Field (FCF), refer to

0x2E

7:6

AACK_FVN_MODE

Controls the ACK behavior, depending on FCF

frame version number