6 start of security operation and status, 7 sram register summary, 8 aes sram configuration register – Rainbow Electronics AT86RF231 User Manual

Page 133

133

8111A–AVR–05/08

AT86RF231

11.1.6

Start of Security Operation and Status

A security operation is started within one SRAM access by appending the start command

AES_REQUEST = 1 (register 0x94, AES_CON_MIRROR) to the SPI sequence. Register

AES_CON_MIRROR is a mirrored version of register 0x83 (AES_CON).

The status of the security processing is indicated by register 0x82 (AES_ST). After 24 µs AES

processing time register bit AES_RY changes to 1 (register 0x82, AES_ST) indicating that the

security operation has finished, see parameter 12.4.15 in

Section 12.4 “Digital Interface Timing

11.1.7

SRAM Register Summary

The following registers are required to control the security module:

These registers are only accessible using SRAM write and read accesses, for details refer to

Section 6.2.3 “SRAM Access Mode” on page 22

. Note, that the SRAM register are reset when

entering the SLEEP state.

11.1.8

AES SRAM Configuration Register

Register 0x82 (AES_ST):

This read-only register signals the status of the security module and operation.

• Bit 7 - AES_ER

This SRAM register bit indicates an error of the AES module. An error may occur for instance

after an access to SRAM register 0x83 (AES_CON) while an AES operation is running or after

reading less than 128 bits from SRAM register space 0x84 - 0x93 (AES_STATE).

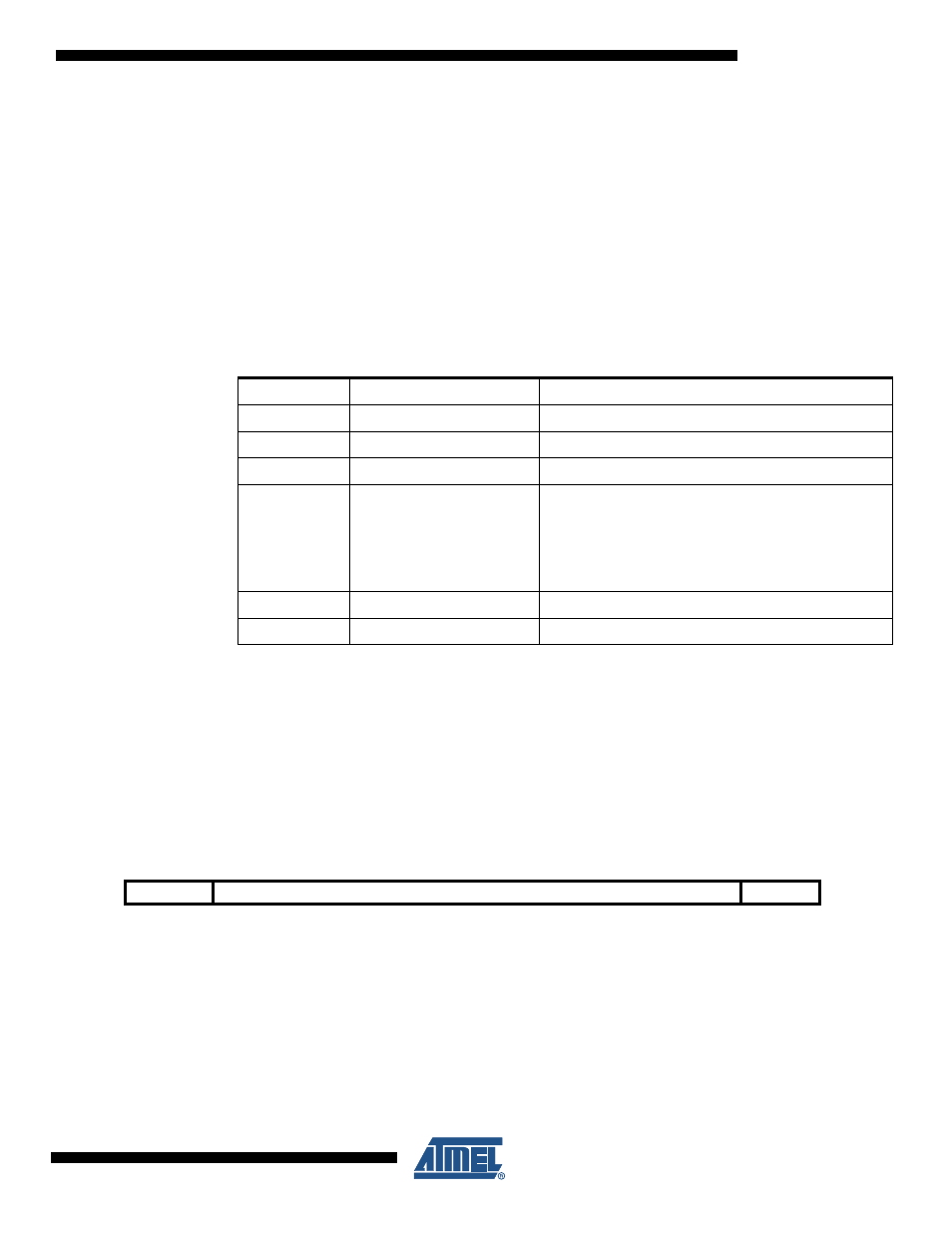

Table 11-2.

SRAM Security Module Address Space Overview

SRAM-Addr.

Register Name

Description

0x80 - 0x81

Reserved, not available

0x82

AES_ST

AES Status

0x83

AES_CON

Security Module Control, AES Mode

0x84 - 0x93

AES_KEY

AES_STATE

Depends on AES_MODE setting:

AES_MODE = 1:

- Contains AES_KEY (key)

AES_MODE = 0 | 2:

- Contains AES_STATE (128 bit data block)

0x94

AES_CON_MIRROR

Mirror of register 0x83 (AES_CON)

0x95 - 0xFF

Reserved, not available

Bit

7

6

5

4

3

2

1

0

+0x82

AES_ER

Reserved

AES_RY

AES_ST

Read/Write

R

R

R

R

R

R

R

R

Reset Value

0

0

0

0

0

0

0

0