Rainbow Electronics AT76C551 User Manual

Single chip bluetooth, Features, System level block diagram

1

Features

•

Implements Bluetooth

™

Specification on Short Distance Wireless Communication in

2.4 GHz ISM Band

•

Provides 1 Mbps Aggregate Bit Rate

•

Supports Frequency Hopping Spread Spectrum Physical-layer Interface to Dedicated

Transceiver with Frequency Hopping Algorithm Implemented in Hardware

•

Provides Baseband Functions in Hardware which Implement Bluetooth Low-level Bit

Processing Such as Forward Error Correction (FEC), Header Error Check (HEC) and

CRC Generation/Checking and Encryption/Decryption

•

Integrated ARM7TDMI

®

RISC Processor

•

Glueless SRAM Interface, Supporting Up to 256K Bytes of Memory

•

Glueless Flash Memory Interface, Supporting Up to 256K Bytes of Nonvolatile Memory

•

Glueless PCMCIA Bus Interface Conforming to PC Card Standard – Feb. 1995

•

USB Interface Conforming to Universal Serial Bus Standard Version 1.1

•

16550 UART Core Offering 32-byte Receive FIFO and Programmable Baud Rate

•

Programmable 8/16-bit Wide External Memory Interface

•

Supports Multiple Reference Clock Frequencies (13.000, 14.400, 16.800, 19.440 MHz)

•

176-lead LQFP

•

3.3V Supply

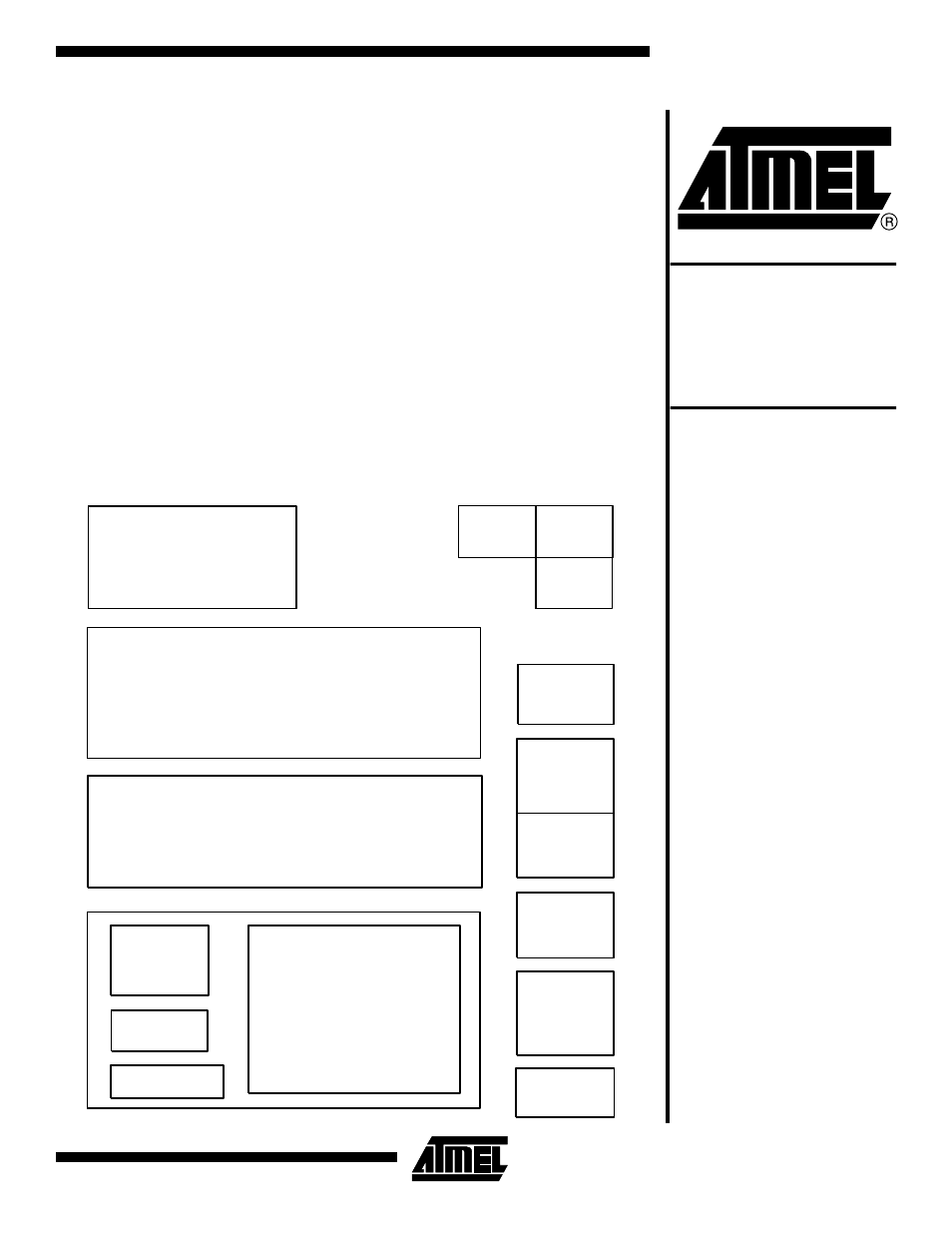

System Level Block Diagram

RSSI

ARM

Clock

Generator

Transmit Data Processing

3-Wire

Control Bus

Memory

Interface

Internal

RAM

PCMCIA

Interface

USB

Slave

AMBA Bus

Interface

Voice

CODEC

Receive Sequencing

Manager

UART

Power

Management

Receive Data Front-end

Receive Data Processing

Single Chip

Bluetooth

™

Controller

AT76C551

Rev. 1612D–08/01

Document Outline

- Features

- System Level Block Diagram

- Overview

- Applications

- Functional Diagram

- Pinout and Package Options

- Pin Summary – Pin Assignment in Numerical Order

- Pin Summary – Pin Assignment in Alphabetical Order

- Signal Description – Pin Name Order

- Functional Description – Pin Name Order

- Internal Architecture

- ARM Core

- Memory Interface

- PCMCIA Interface Unit

- Baseband Processor

- Bluetooth Clock and Internal Hardware Timers

- Frequency Hopping Sequence Generator

- Access Code Generation and Detection

- Forward Error Correction (FEC)

- Header Error Check (HEC)

- Cyclic Redundancy Generation and Check (CRC)

- Encryption/ Decrytion

- Authentication Processing Accelerator

- Receiver Signal Strength Indicator (RSSI)

- 64-byte TX and RX FIFOs

- Baseband TX and RX Processing Sequencer

- 8-bit ADC Interface for Bluetooth RX Data

- Automatic DC- offset Cancellation and Symbol Recovery

- Voice CODEC

- USB Function Interface

- 16550 Compatible UART

- Two 32-bit Timers

- Support for Different Operating Frequencies

- Register Description

- Bluetooth Baseband Register Set

- Voice CODEC Register Set

- USB Registers – USB Wrapper Registers

- UART Register Set

- General Purpose Registers

- Electrical Specifications

- Recommended Operating Conditions

- Absolute Maximum Ratings

- AC Characteristics