7 rx_aack mode timing, 16 µs later. the interrupt latency t – Rainbow Electronics AT86RF231 User Manual

Page 62

62

8111A–AVR–05/08

AT86RF231

7.2.3.6

RX_AACK Slotted Operation - Slotted Acknowledgement

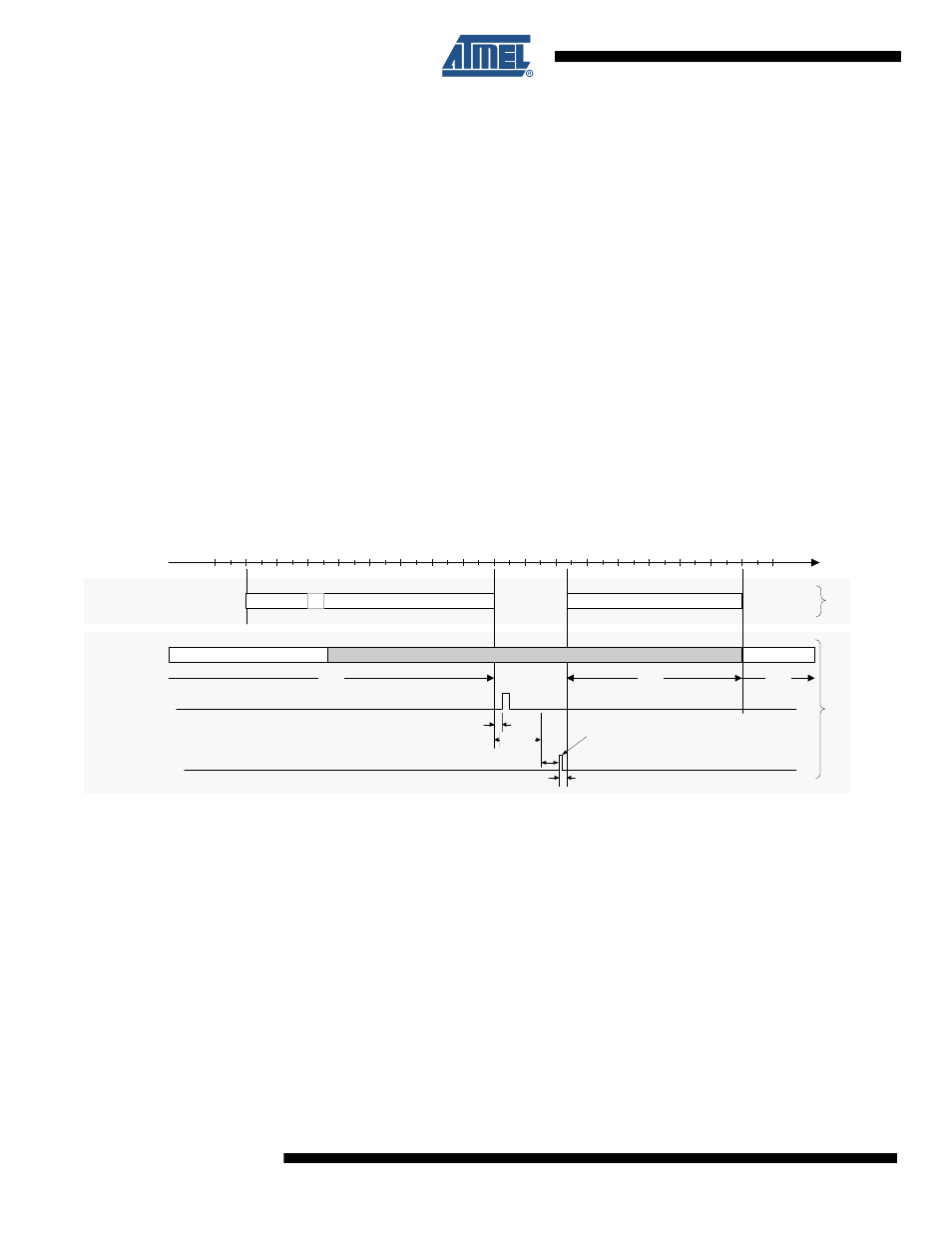

AT86RF231 supports slotted acknowledgement operation, refer to IEEE 802.15.4-2006, section

5.5.4.1, in conjunction with the microcontroller.

In RX_AACK mode with register bit SLOTTED_OPERATION (register 0x2C, XAH_CTRL_0) set,

the transmission of an acknowledgement frame has to be controlled by the microcontroller. If an

ACK frame has to be transmitted, the radio transceiver expects a rising edge on pin 11

(SLP_TR) to actually start the transmission. This waiting state is signaled 6 symbol periods after

the reception of the last symbol of a data or MAC command frame by register bits

TRAC_STATUS (register 0x02, XAH_CTRL_0), which are set to SUCCESS_WAIT_FOR_ACK

in that case. In networks using slotted operation the start of the acknowledgment frame, and

thus the exact timing, must be provided by the microcontroller.

A timing example of an RX_AACK transaction with register bit SLOTTED_OPERATION (register

0x2C, XAH_CTRL_0) set is shown in

. The acknowledgement frame is

ready to transmit 6 symbol times after the reception of the last symbol of a data or MAC com-

mand frame. The transmission of the acknowledgement frame is initiated by the microcontroller

with the rising edge of pin 11 (SLP_TR) and starts t

TR10

= 16 µs later. The interrupt latency t

IRQ

is

Section 12.4 “Digital Interface Timing Characteristics” on page 157

, parameter

12.4.16.

Figure 7-10. Example Timing of an RX_AACK Transaction for Slotted Operation

If register bit AACK_ACK_TIME (register 0x17, XAH_CTRL_1) is set, an acknowledgment frame

can be sent already 2 symbol times after the reception of the last symbol of a data or MAC com-

mand frame.

7.2.3.7

RX_AACK Mode Timing

A timing example of an RX_AACK transaction is shown in

. In this exam-

ple a data frame of length 10 with an ACK request is received. The AT86RF231 changes to state

BUSY_RX_AACK after SFD detection. The completion of the frame reception is indicated by a

TRX_END interrupt. Interrupts IRQ_2 (RX_START) and IRQ_5 (AMI) are disabled in this exam-

ple. The ACK frame is automatically transmitted after a default wait period of 12 symbols

(192 µs), register bit AACK_ACK_TIME = 0 (reset value). The interrupt latency t

IRQ

is specified

in

Section 12.4 “Digital Interface Timing Characteristics” on page 157

, parameter 12.4.16.

RX/TX

F

ram

e

on Ai

r

RX_AACK_ON

TRX_STATE

Frame Type

RX_AACK_ON

RX/TX

RX

TX

TRX_END

IRQ

RX

Typ. Processing Delay

t

IRQ

512

0

704

time [µs]

64

1026

Data Frame (Length = 10, ACK=1)

ACK Frame

SFD

96 µs

(6 symbols)

SLP_TR

t

TR10

TX

RX

SLP_TR

ACK transmission initated by microcontroller

BUSY_RX_AACK

RX

waiting period signalled by register bits TRAC _STATUS