Toshiba H1 SERIES TLCS-900 User Manual

Page 81

TMP92CM22

2007-02-16

92CM22-79

3.6.2

Control Register and Operation after Reset Release

This section describes the registers to control the memory controller, the state after reset

release and necessary settings.

(1) Control register

The control registers of the memory controller are as follows.

• Control register: BnCSH/BnCSL (n = 0 to 3, EX)

Sets the basic functions of the memory controller, that is the connecting

memory type, the number of waits to be read and written.

• Memory start address register: MSARn (n = 0 to 3)

Sets a start address in the selected block address areas.

• Memory address mask register: MAMRn (n = 0 to 3)

Sets a block size in the selected address areas.

In addition to setting of the above-mentioned registers, it is necessary to set the

following registers to control ROM page mode access.

• Page ROM control register: PMEMCR

Sets to executed ROM page mode accessing.

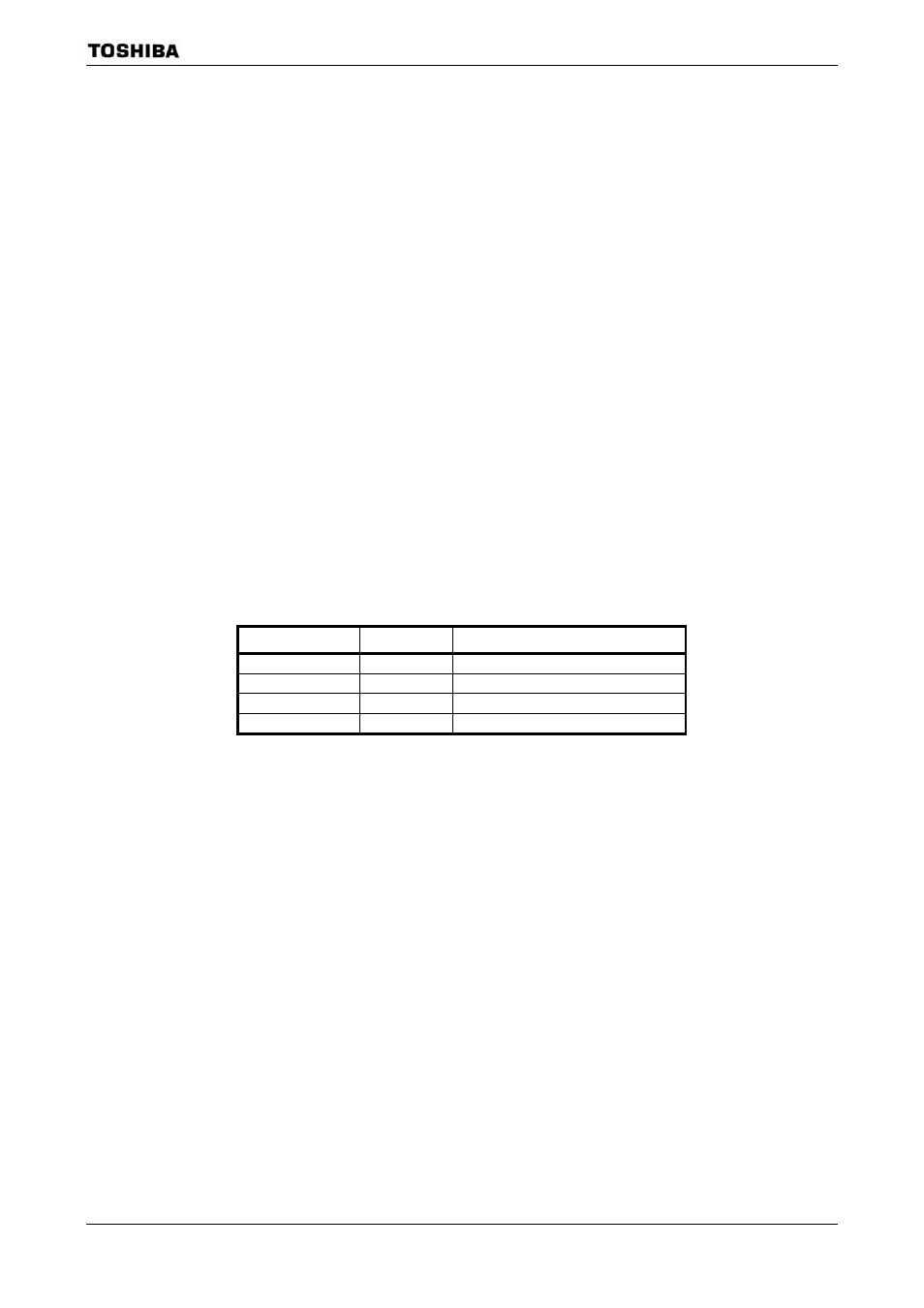

(2) Operation after reset release

The start data bus width is determined depending on state of AM1 and AM0 pins

just after reset release. Then, the external memory is accessed as follows.

AM1 AM0

Start

Mode

0

0

Don’t use this setting

0

1

Start with 16-bit data bus

1

0

Start with 8-bit data bus

1

1

Don’t use this setting

AM1/AM0 pins are valid only just after reset release. In the other cases, the

data bus width is set to the value set to BnBUS bit of the control register.

By reset, only control register (B2CSH/B2CSL) of the block address area 2 is

automatically effective (B2CSH

The data bus width which is specified by AM1/AM0 pin is loaded to the bit to

specify the bus width of the control register in the block address area 2.

The block address area 2 is set to address 000000H to FFFFFFH by reset.

After reset release, the block address areas are specified by the memory start

address register (MSAR) and the memory address mask register (MAMR). Then

the control register (BnCS) is set.

Set the enable bit (BnE) of the control register to “1” to enable the setting.