1) interrupt priority setting registers – Toshiba H1 SERIES TLCS-900 User Manual

Page 42

TMP92CM22

2007-02-16

92CM22-40

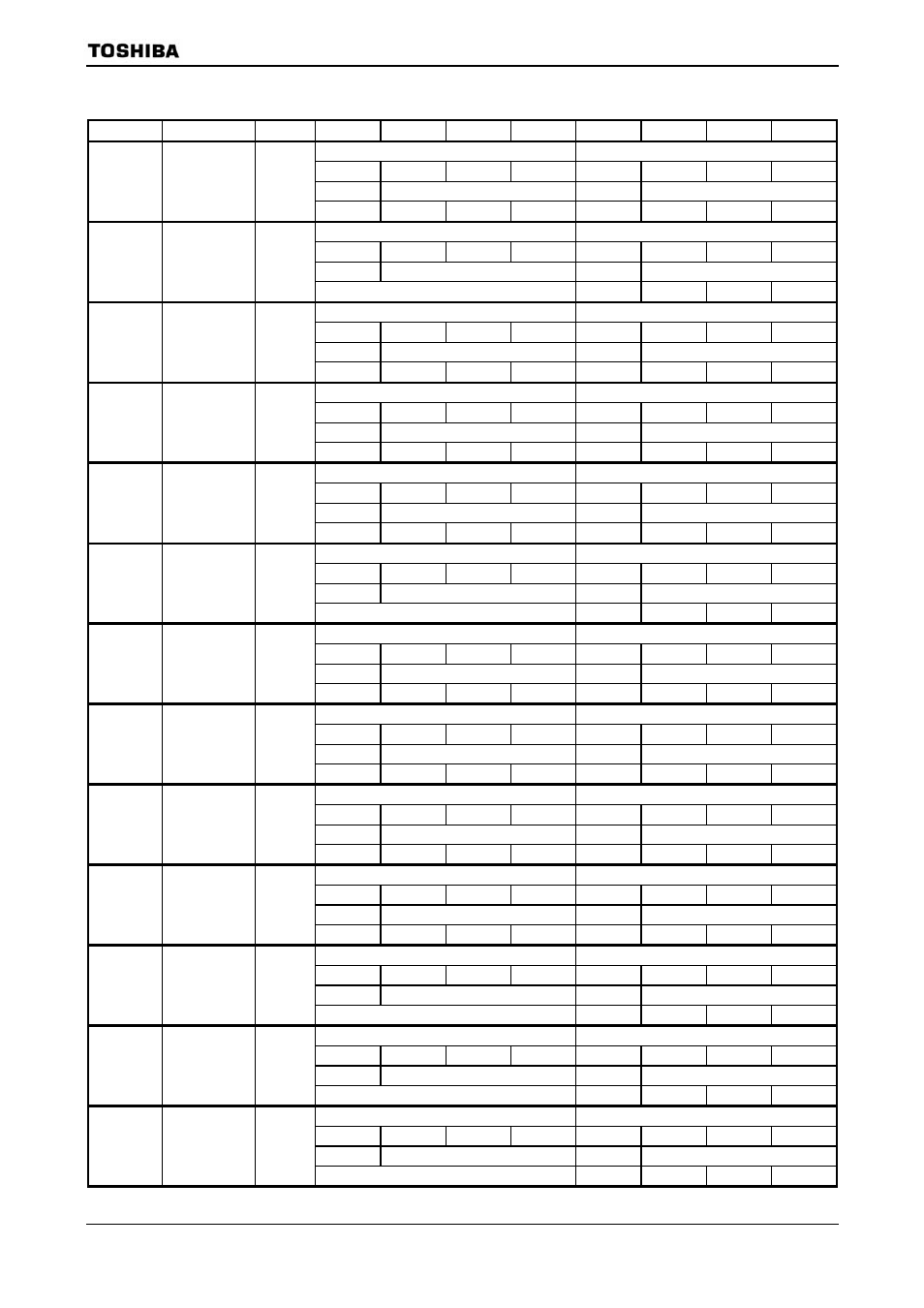

(1) Interrupt priority setting registers

Symbol

Name

Address

7 6 5 4 3 2 1 0

INT2 INT1

I2C I2M2 I2M1 I2M0 I1C I1M2 I1M1 I1M0

R R/W R R/W

INTE12

INT1&INT2

enable

D0H

0 0 0 0 0 0 0 0

− INT3

−

−

−

− I3C

I3M2

I3M1

I3M0

−

− R

R/W

INTE3

INT3

enable

D1H

Note: Always write “0”.

0

0

0

0

INTTA1 (TMRA1)

INTTA0 (TMRA0)

ITA1C ITA1M2

ITA1M1

ITA1M0

ITA0C ITA0M2 ITA0M1 ITA0M0

R R/W R R/W

INTETA01

INTTA0&

INTTA1

enable

D4H

0 0 0 0 0 0 0 0

INTAT3 (TMRA3)

INTAT2 (TMRA2)

ITA3C ITA3M2

ITA3M1

ITA3M0

ITA2C ITA2M2 ITA2M1 ITA2M0

R R/W R R/W

INTETA23

INTTA2&

INTTA3

enable

D5H

0 0 0 0 0 0 0 0

INTTB01 (TMRB0)

INTTB00 (TMRB0)

ITB01C ITB01M2

ITB01M1

ITB01M0

ITB00C

ITB00M2 ITB00M1

ITB00M0

R R/W R R/W

INTETB0

INTTB00&

INTTB01

enable

D8H

0 0 0 0 0 0 0 0

− INTTBO0

(TMRB0)

−

−

−

− ITBO0C

ITBO0M2

ITBO0M1

ITBO0M0

R R/W R R/W

INTETBO0

INTTBO0

(Overflow)

enable

DAH

Note: Always write “0”.

0

0

0

0

INTTX0 INTRX0

ITX0C ITX0M2

ITX0M1

ITX0M0

IRX0C

IRX0M2 IRX0M1 IRX0M0

R R/W R R/W

INTES0

INTRX0&

INTTX0

enable

DBH

0 0 0 0 0 0 0 0

INTTX1 INTRX1

ITX1C ITX1M2

ITX1M1

ITX1M0

IRX1C

IRX1M2 IRX1M1 IRX1M0

R R/W R R/W

INTES1

INTRX1&

INTTX1

enable

DCH

0 0 0 0 0 0 0 0

INT5 INT4

I5C I5M2 I5M1 I5M0 I4C I4M2 I4M1 I4M0

R R/W R R/W

INTE45

INT4&

INT5

enable

E0H

0 0 0 0 0 0 0 0

INTTB11 (TMRB1)

INTTB10 (TMRB1)

ITB11C ITB11M2

ITB11M1

ITB11M0

ITB10C

ITB10M2 ITB10M1

ITB10M0

R R/W R R/W

INTETB1

INTTB10&

INTTB11

enable

E1H

0 0 0 0 0 0 0 0

− INTTBO1

(TMRB1)

−

−

−

− ITBO1C

ITBO1M2

ITBO1M1

ITBO1M0

−

− R

R/W

INTETBO1

INTTBO1

(Overflow)

enable

E2H

Note: Always write “0”.

0

0

0

0

− INTSBE0

−

−

−

−

ISBE0C

ISBE0M2 ISBE0M1

ISBE0M0

−

− R

R/W

INTESB0

INTSBE0

enable

E3H

Note: Always write “0”.

0

0

0

0

− INTP0

−

−

−

− IP0C

IP0M2

IP0M1

IP0M0

−

− R

R/W

INTEP0

INTP0

enable

EEH

Note: Always write “0”.

0

0

0

0