Toshiba H1 SERIES TLCS-900 User Manual

Page 167

TMP92CM22

2007-02-16

92CM22-165

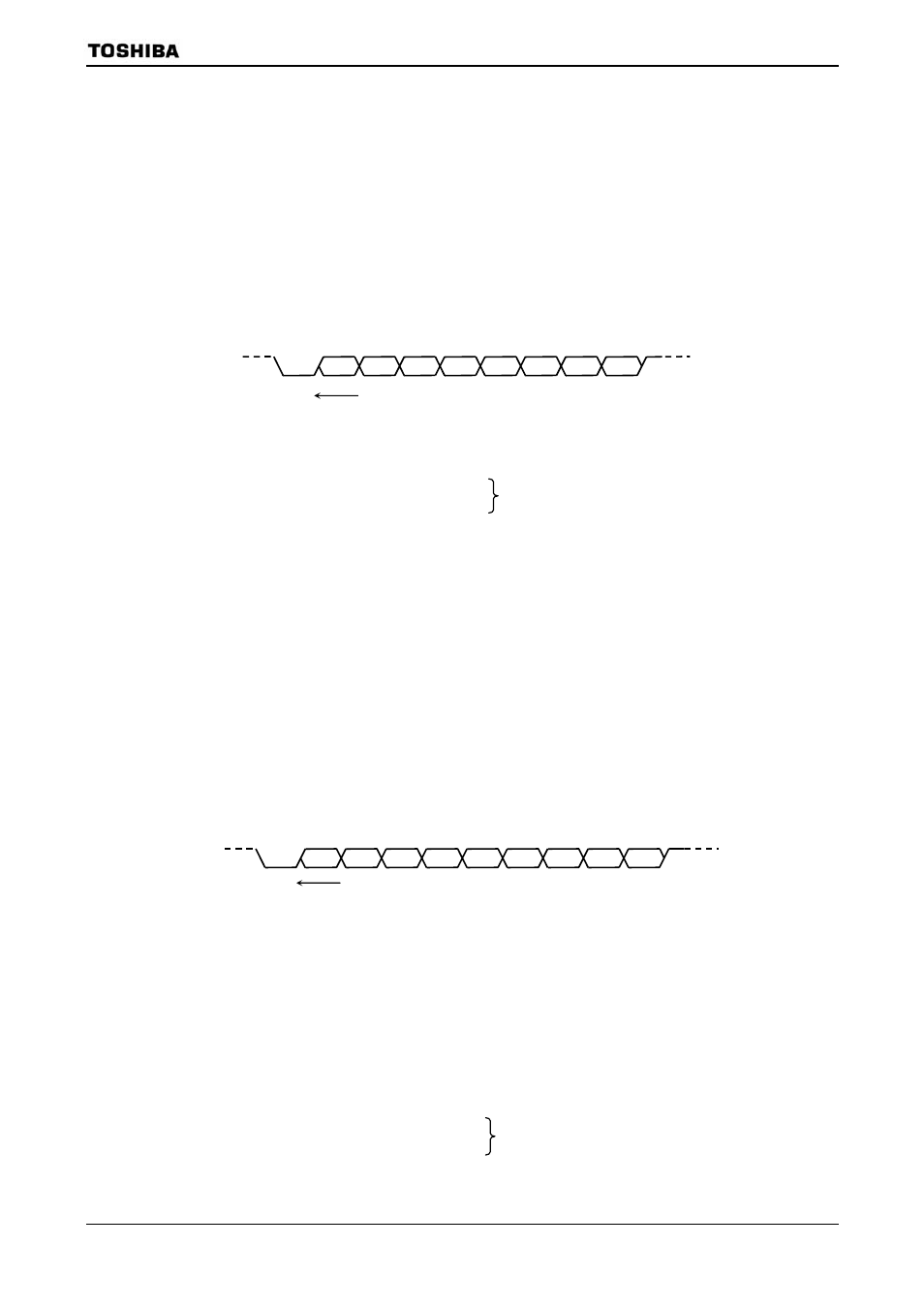

(2) Mode 1 (7-bit UART mode)

7-bit UART mode is selected by setting serial channel mode register

SC0MOD0

In this mode, a parity bit can be added. Use of a parity bit is enabled or disabled by

the setting of the serial channel control register SC0CR

or odd parity will be used is determined by the SC0CR

SC0CR

Example: When transmitting data of the following format, the control registers should be

set as described below. This explanation applies to channel 0

.

Transfer direction (Transfer speed 2400 bps at f

C

= 39.3216 MHz)

* Clock state:

Clock gear 1/1(fc)

7

6

5

4

3

2

1

0

PFCR

← − − − − − − − 1

PFFC

← − − − − − − − 1

Set PF0 to as TXD0 pin.

SC0MOD

← X 0 − X 0 1 0 1

Set to 7-bit UART mode.

SC0CR

← X 1 1 X X X 0 0

Add

even

parity.

BR0CR

← 0 0 1 0 1 0 0 0

Set to 2400 bps.

INTES0

← 1 1 0 0 − − − −

Set INTTX0 interrupt to enable, set to level 4.

SC0BUF

← ∗ ∗ ∗ ∗ ∗ ∗ ∗ ∗ Set

transmission

data.

X : Don’t care,

− : No change

(3) Mode 2 (8-bit UART mode)

8-bit UART mode is selected by setting SC0MOD0

parity bit can be added (Use of a parity bit is enabled or disabled by the setting of

SC0CR

SC0CR

Example: When receiving data of the following format, the control registers should be set

as described below.

* Clock state:

Clock gear 1/1(fc)

Main

routine

7

6

5

4

3

2

1

0

PFCR

← − − − − − − 0 −

Set PF1 (RXD0) to input pin.

SC0MOD

← − 0 1 X 1 0 0 1

Set to 8-bit UART mode, set receives to enable.

SC0CR

← X 0 1 X X X 0 0

Add

odd

parity.

BR0CR

← 0 0 0 1 1 0 0 0

Set to 9600 bps.

INTES0

← − − − − 1 1 0 0

Set INTTX0 interrupt to enable, set to level 4.

Interrupt

routine

processing

Acc

← SC0CR AND 00011100

if

Acc

≠ 0 then ERROR

Check for error.

Acc

← SC0BUF

Read receiving data.

X : Don’t care,

− : No change

Stop

Even

parity

6

5

4

3

2

1

Bit0

Start

Start

Bit0

1

2

3

4

5

6

Transfer direction (Transfer speed 9600 bps at f

C

= 39.3216 MHz)

Odd

parity

Stop

7