1 block diagrams – Toshiba H1 SERIES TLCS-900 User Manual

Page 102

TMP92CM22

2007-02-16

92CM22-100

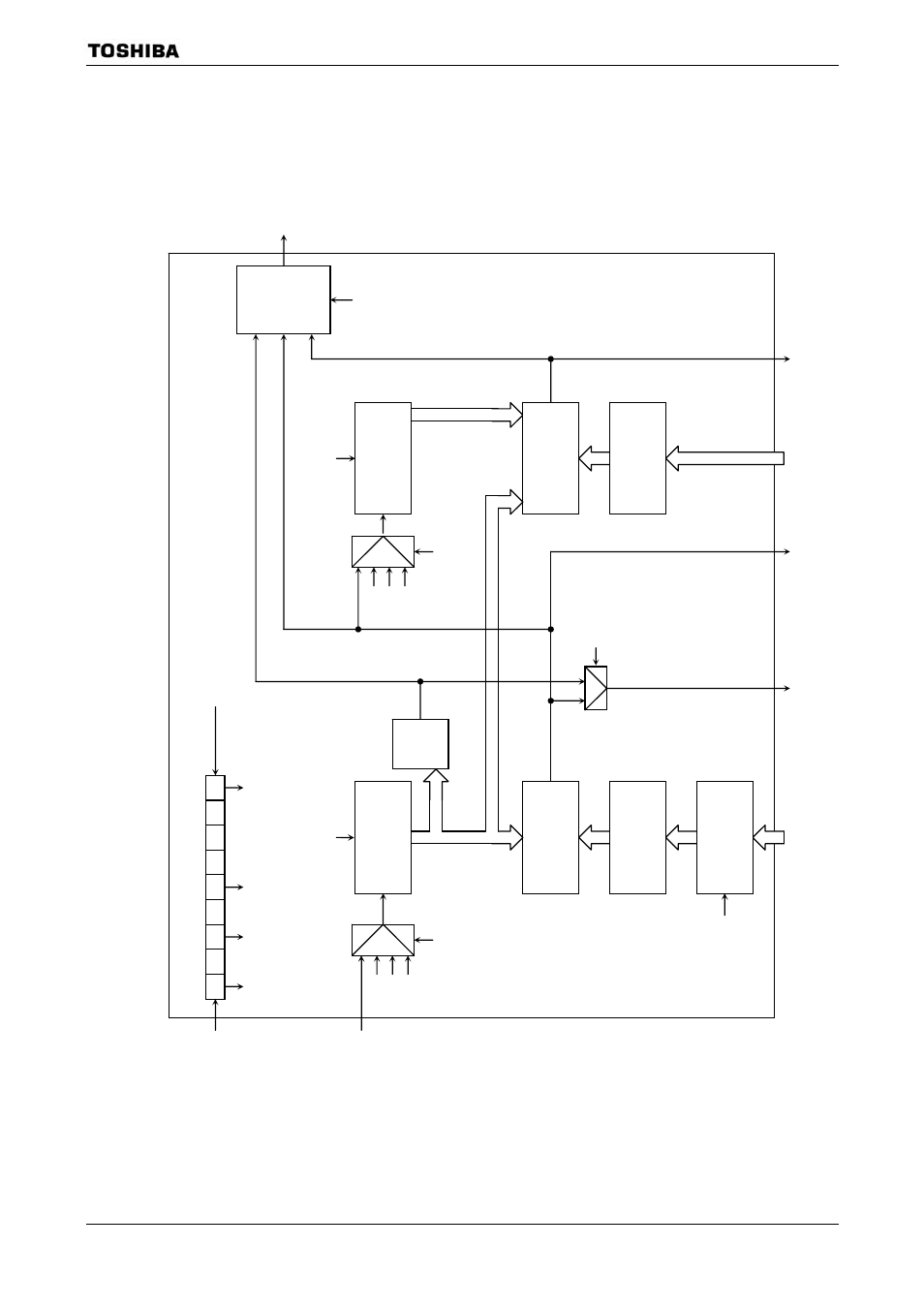

3.7.1 Block

Diagrams

Figure 3.7.1 TMRA01 Block Diagram

φT1

φT16

φT256

8-bit comparato

r

(CP1)

8-bit comparato

r

(CP0)

8-bit up counter

(UC0

)

2

n

over

flo

w

8-bit up counter

(UC1

)

Ti

mer

flip-

flop

TA1FF

Match

detect

Match

detect

8-bit timer regist

er

TA1REG

φT1

φT4

φT16

512

256

128

64

32

16

8

4

2

φT1

φT4

φT16

φT256

Run/clea

r

Pr

escale

r

External input

clock: T

A0IN

TA01MOD

Pr

escale

r

clock:

φT0

TA01RU

N

RUN> Selecto r 8-bit timer regist er TA0REG TA01MOD TA01MOD TMRA0 interrupt out put: INTTA0 TMRA0 match output : TA0TR G TA01MOD TA01RU N RUN> TA1FF CR T imer flip- flop output: T A 1 O U T TMRA1 interrupt out put: INTTA1 Internal data b u s TA01RU N TA01RU N Selecto r Internal data b u s TA0TR G Register buffer 0