1 block diagram – Toshiba H1 SERIES TLCS-900 User Manual

Page 145

TMP92CM22

2007-02-16

92CM22-143

3.9.1 Block

Diagram

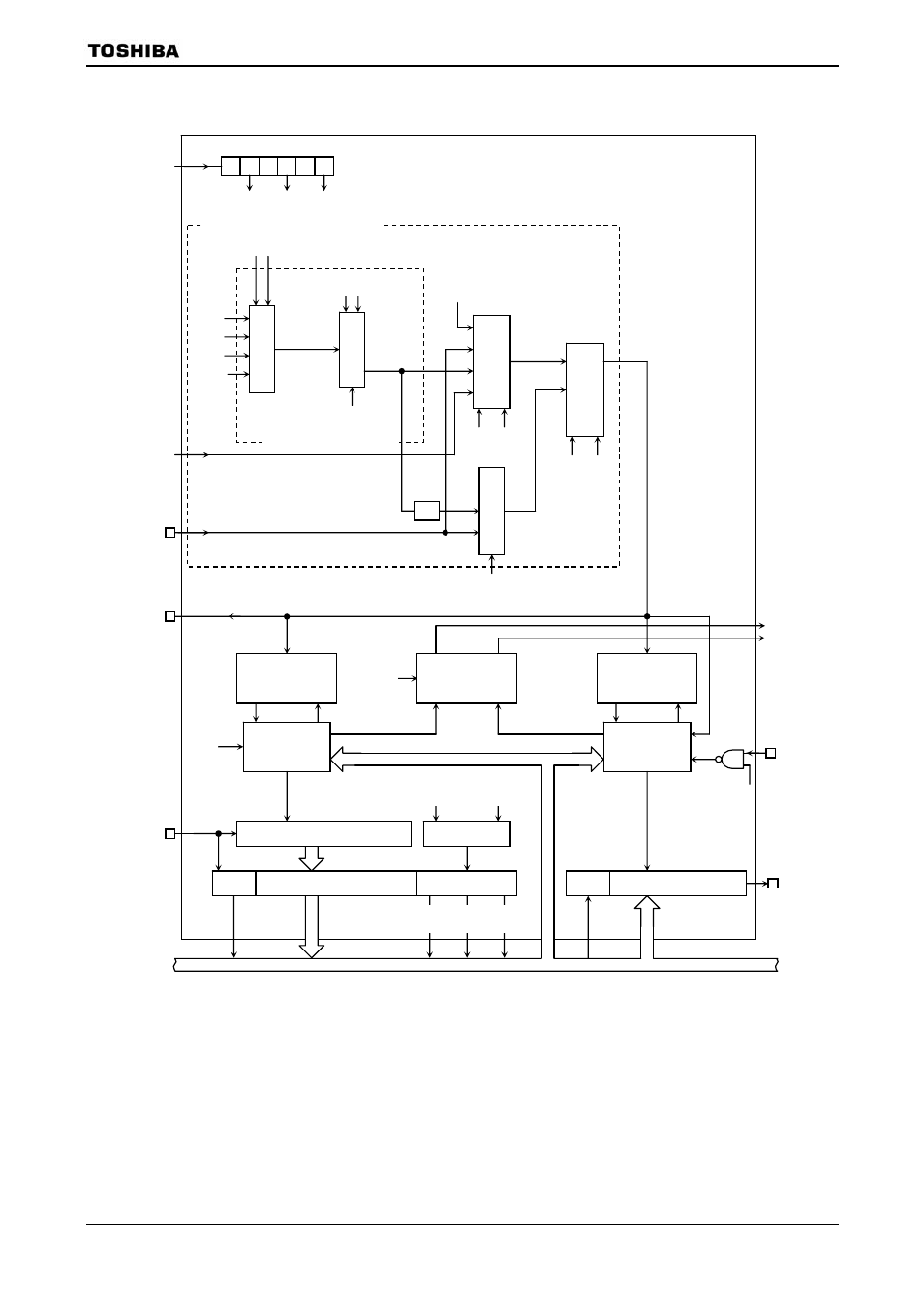

Figure 3.9.2 Block Diagram of SIO0

Selector

φT0

φT2

φT8

φT32

SC0MOD0

Receive buffer 1 (Shift register)

RXDCLK

SC0MOD0

Pr

escaler

Selector

TA0TRG

(from TMRA0)

UART

mode

BR0CR

Baud rate generater

Selector

SC0MOD0

Selector

÷ 2

I/O interface mode

SC0CR

Receive counter

(UART only

÷ 16)

Transmission

counter

(UART only

÷ 16)

Receive control

Transsmission

control

INTRX0

INTTX0

Receive buffer 2 (SC0BUF)

RB8

Error flag

SC0CR

Serial channel

interrupt control

TB8

CTS0

(Shared with PF2)

TXD0

(Shared with PF0)

Transmission

buffer

(SC0BUF)

RXD0

(Shared

with PF1)

TXDCLK

SC0MOD0

f

io

SC0MOD0

SCLK0 output

(Shared

with PF2)

SCLK0 input

(Shared

with PF2)

SIOCLK

Internal data bus

Parity control

SC0CR

Serial clock generation circuit

BR0CR

BR0ADD

BR0CR

I/O interface mode

φT0

2

64

4 8 16 32

Prescaler

φT2 φT8 φT32

Interrupt