Toshiba H1 SERIES TLCS-900 User Manual

Page 178

TMP92CM22

2007-02-16

92CM22-176

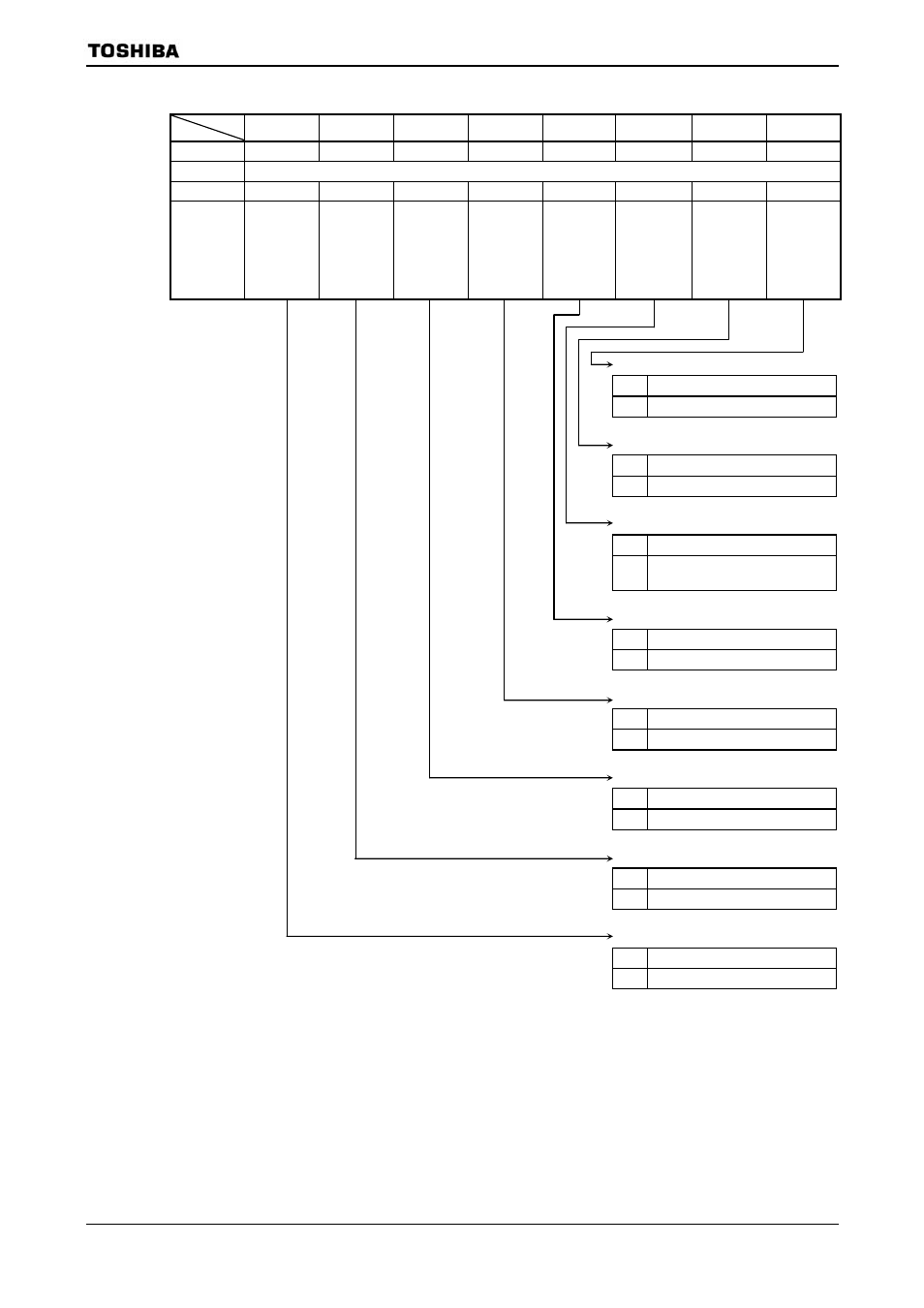

Serial Bus Interface Status Register

7 6 5 4 3 2 1 0

Bit symbol

MST

TRX

BB PIN AL AAS AD0 LRB

SBI0SR

(1243H)

Read/Write R

After

reset

0 0 0 1 0 0 0 0

Read-

modify-write

instruction is

prohibited.

Function Master/

slave

status

selection

monitor

Transmitter/

receiver

status

selection

monitor

I

2

C bus

status

monitor

INTSBE0

interrupt

request

monitor

Arbitration

lost

detection

monitor

0:

−

1: Detected

Slave address

match

detection

monitor

0: Undetected

1: Detected

GENERAL

CALL

detection

monitor

0: Undetected

1: Detected

Last

received bit

monitor

0: 0

1: 1

0

Last received bit was 0.

1

Last received bit was 1.

0

Undetected

1

GENERAL CALL detected

0

Undetected

1

Slave address match or

GENERAL CALL detected

0

−

1

Arbitration lost

0

Interrupt requested

1

Interrupt released

0

Free

1

Busy

0

Receiver

1

Transmitter

0

Slave

1

Master

Note: Writing in this register functions as SBI0CR2.

Figure 3.10.5 Register for I

2

C Bus Mode

Last received bit monitor

GENERAL CALL detection monitor

Slave address match detection monitor

Arbitration lost detection monitor

INTSBE0 interrupt request monitor

Transmitter/receiver status monitor

Master/slave status monitor

I

2

C bus status monitor