Toshiba H1 SERIES TLCS-900 User Manual

Page 37

TMP92CM22

2007-02-16

92CM22-35

Although the control registers used for setting the transfer source and transfer

destination addresses are 32 bits wide, this type of register can only output 24-bit

addresses. Accordingly, micro DMA can only access 16 Mbytes (the upper eight bits of a

32-bit address are not valid).

Three micro DMA transfer modes are supported: one-byte transfers, two-byte

(one-word) transfer and four-byte transfer. After a transfer in any mode, the transfer

source and transfer destination addresses will either be incremented or decremented,

or will remain unchanged. This simplifies the transfer of data from memory to memory,

from I/O to memory, from memory to I/O, and from I/O to I/O. For details of the various

transfer modes, see section 3.4.2 (1), detailed description of the transfer mode register.

Since a transfer counter is a 16-bit counter, up to 65536 micro DMA processing

operations can be performed per interrupt source (provided that the transfer counter

for the source is initially set to 0000H).

Micro DMA processing can be initiated by any one of 34 different interrupts – the 33

interrupts shown in the micro DMA start vectors in Table 3.4.1 and a micro DMA soft

start.

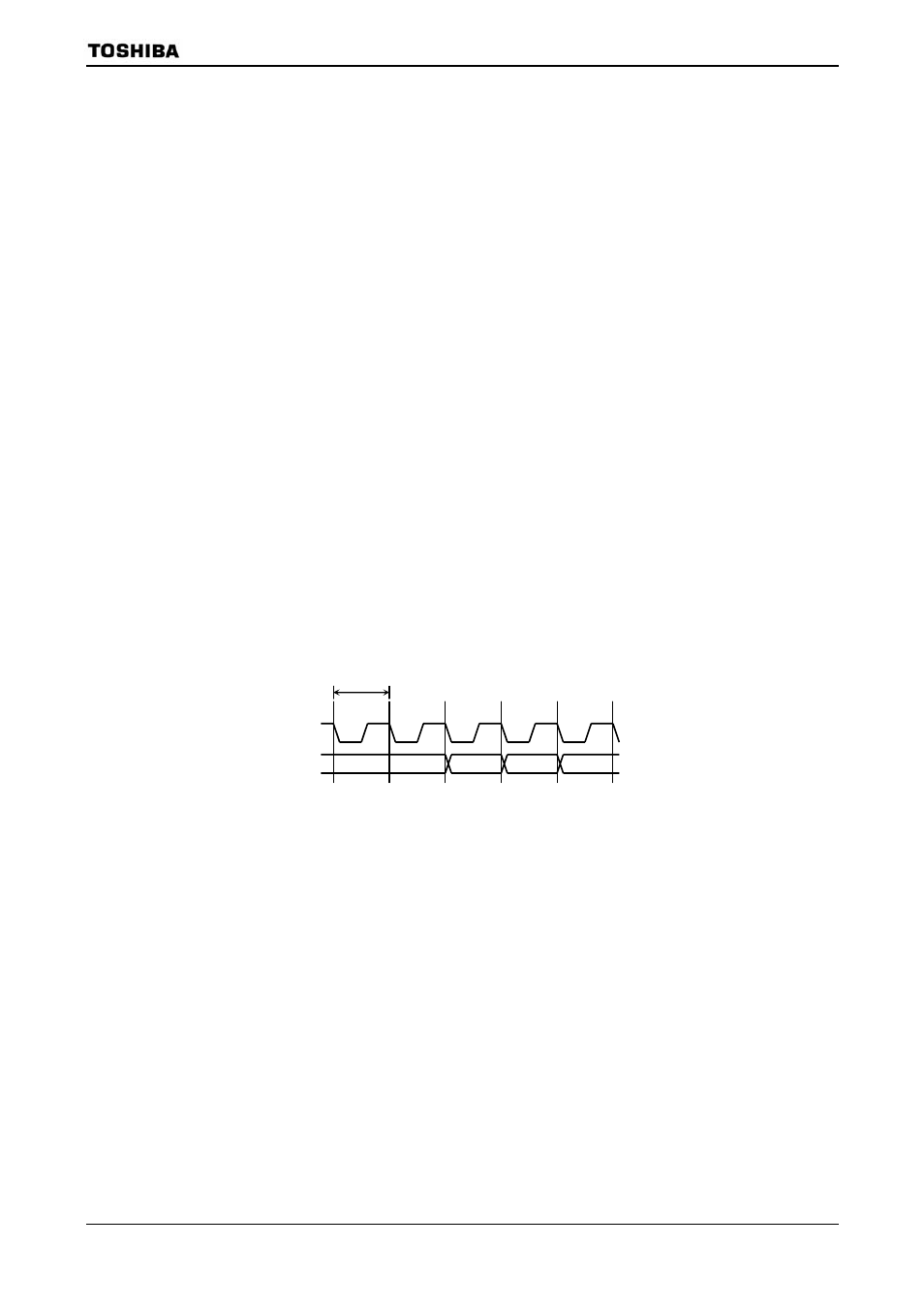

Figure 3.4.2 shows a 2-byte transfer carried out using a micro DMA cycle in transfer

destination address INC mode (micro DMA transfers are the same in every mode

except counter mode). (The conditions for this cycle are as follows: Both source and

destination memory are internal RAM and multiples by 4 numbered source and

destination addresses.)

Figure 3.4.2 Timing for Micro DMA Cycle

States 1 to 2:

Instruction fetches cycle (Gets next address code).

If the instruction queue buffer is FULL , this cycle becomes a dummy

cycle.

State 3:

Micro DMA read cycle.

State 4:

Micro DMA writes cycle.

State 5:

(The same as in state 1, 2.)

a. b.

c.

d.

e.

dst

src

A0 to A23

CLK

1 state