Toshiba H1 SERIES TLCS-900 User Manual

Page 5

TMP92CM22

2007-02-16

92CM22-3

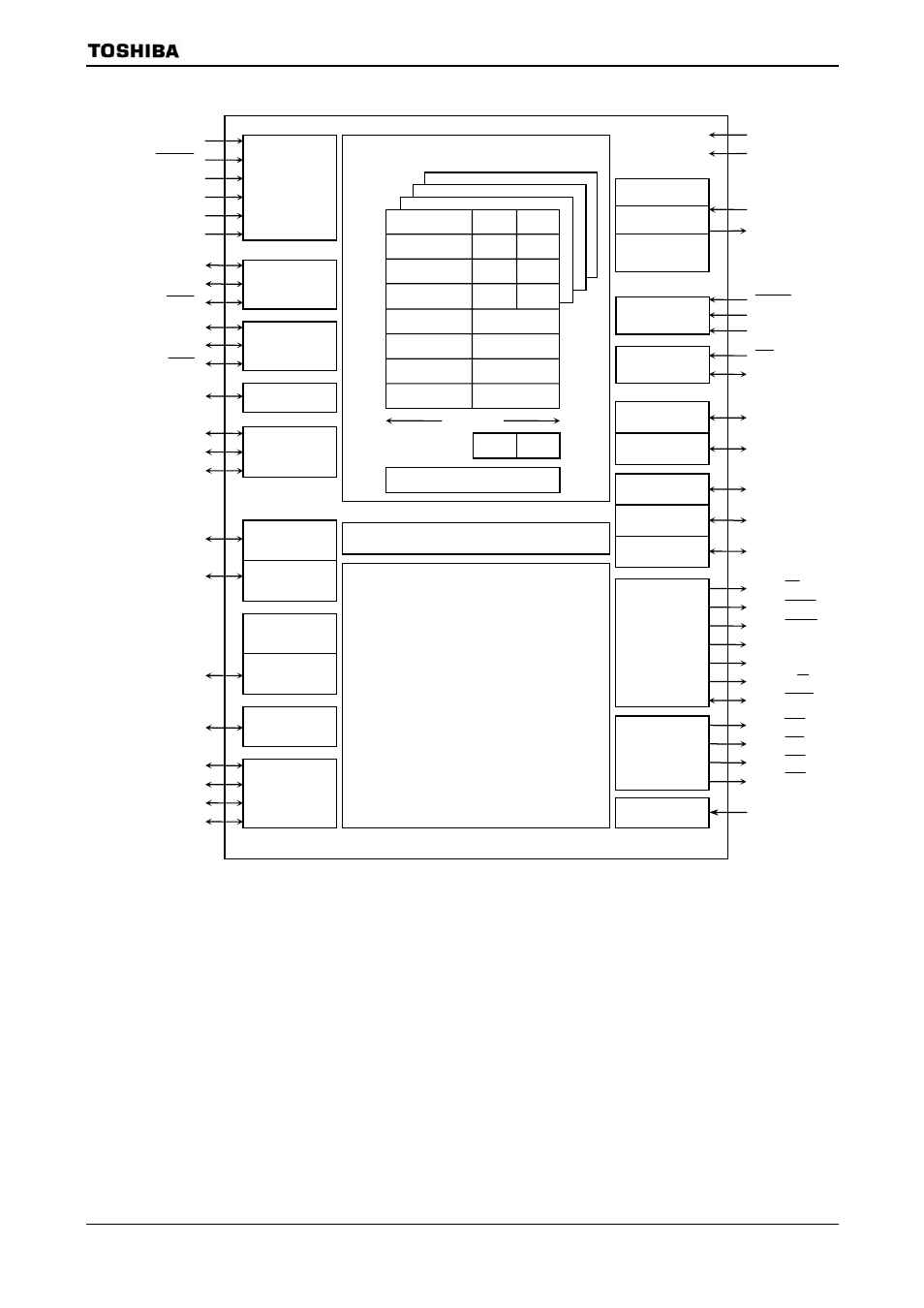

Figure 1.1 TMP92CM22 Block Diagram

XSP

XIZ

XIY

XIX

XHL

XDE

XBC

XWA

900/H1 CPU

F

SR

32 bits

IX

IY

IZ

SP

L

H

E

D

C

B

A

W

P C

32-Kbyte RAM

Serial I/O

SIO0

PF1 (RXD0)

PF0 (TXD0)

DVSS [4]

DVCC [3]

Mode

controller

RESET

AM0

AM1

Data bus

D0 to D7

Port 5

10-bit 8-ch

AD

converter

VREFL

VREFH

AVSS

AVCC

PG0 to PG7

(AN0 to AN7)

8-bit timer

(Timer A0)

PC0 (TA0IN)

8-bit timer

(Timer A1)

PC1 (TA1OUT/INT1)

Watchdog timer

Port 7

P76 (

WAIT

)

P70 (

RD

)

P71 (

WRLL

)

Interrupt

controller

PC3(INT0)

NMI

Port 1

Port 4

Port 6

Port 8

P10 to P17

(D8 to D15)

P40 to P47

(A0 to A7)

P50 to P57

(A8 to A15)

P60 to P67

(A16 to A23)

P75 (R/

W

)

8-bit timer

(Timer A2)

8-bit timer

(Timer A3)

PC5 (TA3OUT/INT2)

P80 (

CS0

)

P82 (

CS2

)

P72 (

WRLU

)

P73

P74 (CLKOUT)

P81 (

CS1

)

P83 (

CS3

)

Serial

bus I/F

SBI0

P90 (SCK)

P92 (SI/SCL)

P91 (SO/SDA)

PG3 (

ADTRG

)

16-bit timer

(Timer B1)

PD2 (TB1OUT0)

PD1 (TB1IN1/INT5)

PD0 (TB1IN0/INT4)

PD3 (TB1OUT1)

Port F

PF6 to PF7

X1

X2

PLL

PA0 to PA2

PA7

Port A

H-OSC

Clock gear

PF2 (SCLK0/

CTS0

)

Serial I/O

SIO1

PF4 (RXD1)

PF3 (TXD1)

PF5 (SCLK1/

CTS1

)

16-bit timer

(Timer B0)

PC6 (TB00UT0/INT3)