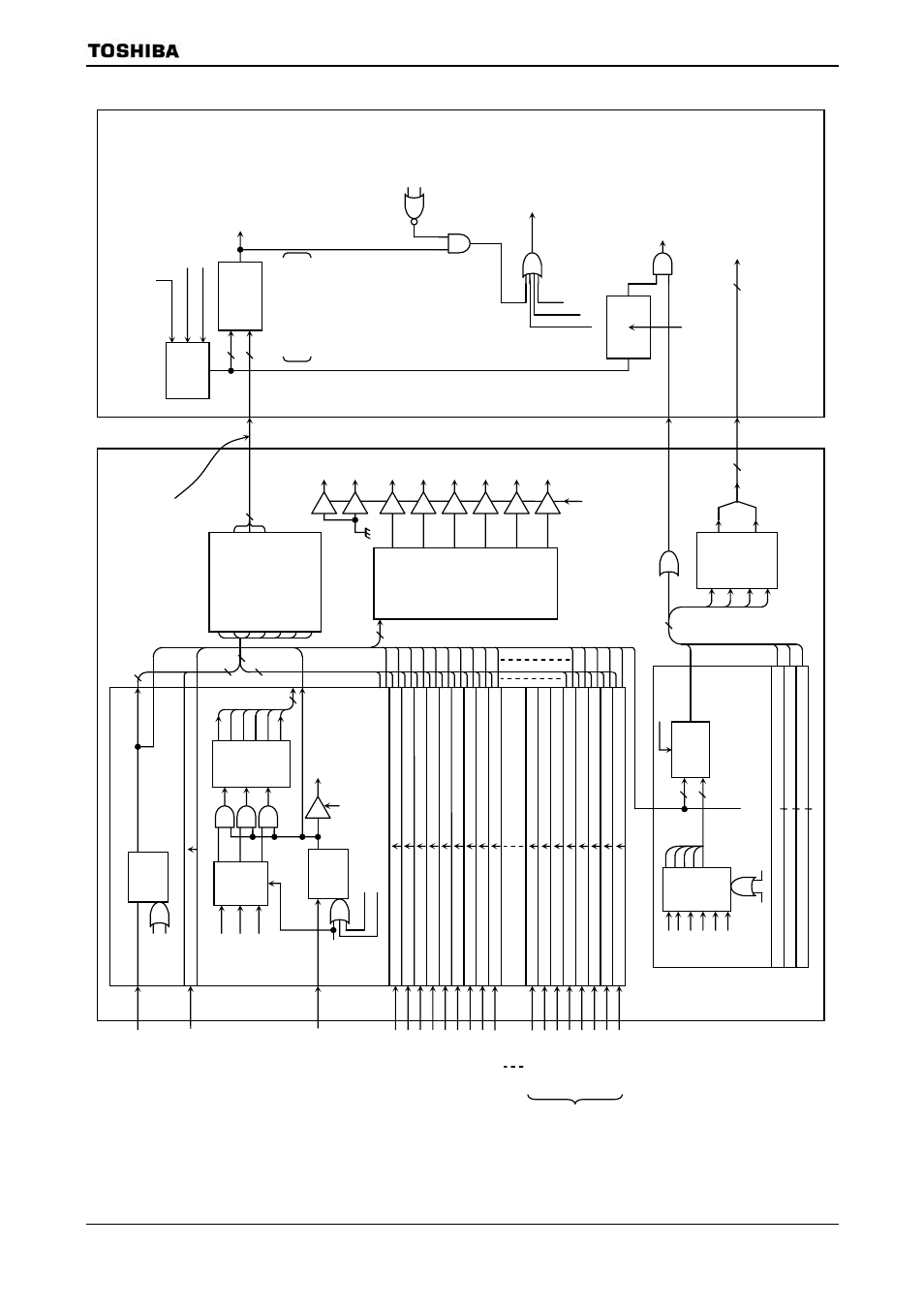

Figure 3.4.3 block diagram of interrupt controller – Toshiba H1 SERIES TLCS-900 User Manual

Page 41

TMP92CM22

2007-02-16

92CM22-39

Figure 3.4.3 Block Diagram of Interrupt Controller

Interrup

t request

signal to CPU

M

icro DM

A

s

tar

t ve

cto

r set

ting

reg

is

ter

During

ST

OP

36

3

3

3

1

6

2

2

4

6

34

4-input OR

INT0 to I

NT3

Micro DMA channel

p

ri

ori

ty

encode

r

Priority encode

r

DMA0V

DMA1V

DMA2V

DMA3V

Reset

Interrup

t request

flag

Reset

Re

set

Priorit

y

settin

g

re

g

iste

r

V

= 20H

V

= 24H

Interrup

t controlle

r

CPU

S Q

R

V

= 28H

V

= 2CH

V

= 30H

V

= 34H

V

= 38H

V

= 3CH

V

= 40H

V

= 44H

V

= 48H

V

= 4CH

V

= D0H

V

= D4H

V

= D8H

V

= DC

H

V

= E0H

V

= E4H

V

= E8H

V

= ECH

D Q

CLR

A

B

C

Dn

Dn

+ 1

Dn

+ 2

Interrup

t

request flag

Interrup

t vector r

ead

Micro DMA acknowlege

Interrup

t

req

uest F/F read

Dn

+ 3

A

B

C

In

terrup

t

vector read

D2

D3

D4

D5

D6

D7

0

1

2

3

A

B

D0

D1

Interrup

t enable

flag in CPU side

Micro DMA

requ

est

Relea

s

e

hal

t

INT

R

Q2

to

0

≥

I

FF

2 to

0

th

en1

INTR

Q2 to

0

IFF2:0

Reset

EI1 to 7

DI

Interrup

t request

signal

Micro DMA

channel

specificat

ion

RESET

INTWD

INT0

INT1

INT2

INT3

(Re

s

er

ved)

(Re

s

er

ved)

(Re

s

er

ved)

(Re

s

er

ved)

(Re

s

er

ved)

(Re

s

er

ved)

INTT

C0

INTT

C1

INTT

C2

INTT

C3

INTT

C4

INTT

C5

INTT

C6

INTT

C7

Interrup

t

vector

generato

r

Highe

st

priority interrupt

level

select

1

2

3

4

5

6

7

D5

D4

D3

D2

D1

D0

Decode

r

Y1

Y2

Y3

Y4

Y5

Y6

S Q

R

7

1

6

(Highe

st p

riori

ty

is “

7

”.)

Interuupt

level detect

D Q

CLR

S

Selector

Interrup

t vector V

read

INTT

C0

Soft start

Micro DMA

counte

r 0

interrupt

If IFF

=

7 then 0

NMI

(Re

s

er

ved)

During

IDL

E

1