Toshiba H1 SERIES TLCS-900 User Manual

Page 27

TMP92CM22

2007-02-16

92CM22-25

(3) Operation

a. IDLE2 mode

In IDLE2 mode only specific internal I/O operations, as designated by the

IDLE2 setting register, can take place. Instruction execution by the CPU stops.

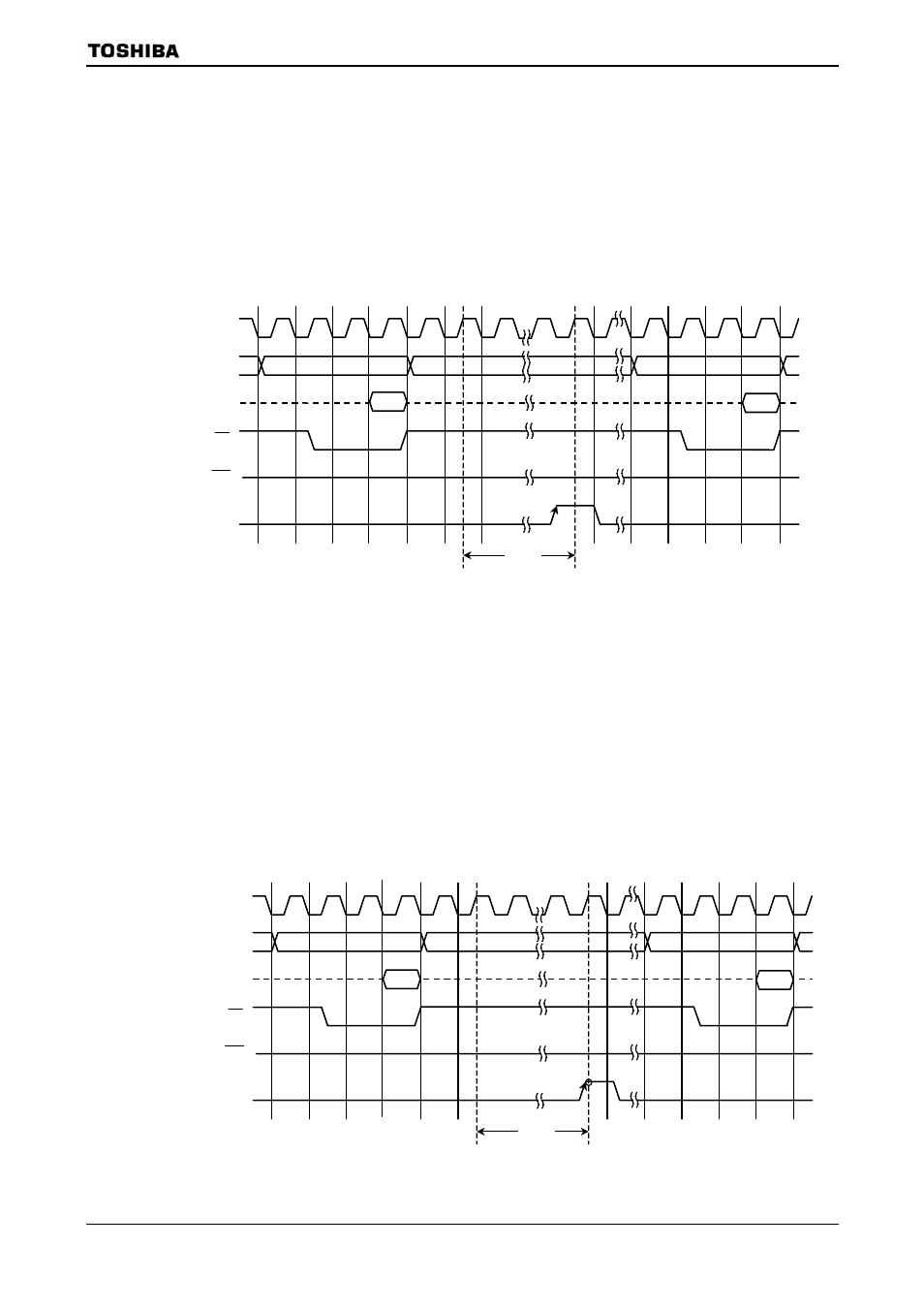

Figure 3.3.6 illustrates an example of the timing for clearance of the IDLE2

mode halt state by an interrupt.

Interrupt of

releasing halt

IDLE2

mode

Data

Data

X1

A0 to A23

D0 to D15

RD

WR

Figure 3.3.6 Timing Chart for IDLE2 Mode Halt State Released by Interrupt

b. IDLE1 mode

In IDLE1 mode, only the internal oscillator operates. The system clock stops.

And, pin state in IDLE1 mode depend on setting SYSCR2

register. Table 3.3.5, Table 3.3.6 shows pin state in IDLE1 mode.

In the halt state, the interrupt request is sampled asynchronously with the

system clock; however, clearance of the halt state (e.g., restart of operation) is

synchronous with it.

Figure 3.3.7 shows the timing for release of the IDLE1 mode halt state by an

interrupt.

IDLE1

mode

Data

Data

X1

A0 to A23

D0 to D15

RD

WR

Interrupt of

releasing halt

Figure 3.3.7 Timing Chart for IDLE1 Mode Halt State Released by Interrupt