5 control in i2c bus mode, 5 control in i, C bus mode – Toshiba H1 SERIES TLCS-900 User Manual

Page 180

TMP92CM22

2007-02-16

92CM22-178

3.10.5 Control in I

2

C Bus Mode

(1) Acknowledge mode specification

Set the SBI0CR1

TMP92CM22 generates an additional clock pulse for an acknowledge signal when

operating in master mode. In the transmitter mode during the clock pulse cycle, the

SDA pin is released in order to receive the acknowledge signal from the receiver. In the

receiver mode during the clock pulse cycle, the SDA pin is set to the low in order to

generate the acknowledge signal.

Clear the

does not generate a clock pulse for the acknowledge signal when operating in the

master mode.

(2) Select number of transfer bits

The SBI0CR1

receiving data.

Since the

direction bit are transferred in 8 bits. Other than these, the

specified value.

(3) Serial clock

1. Clock

source

The SBI0CR1

on the SCL pin in master mode. Set the baud rates, which have been calculated

according to the formula below, to meet the specifications of the I

2

C bus, such as the

smallest pulse width of t

LOW

.

SBI0CR1

000 5

001 6

010 7

011 8

100 9

101 10

110 11

Note: f

SBI

shows f

SYS

.

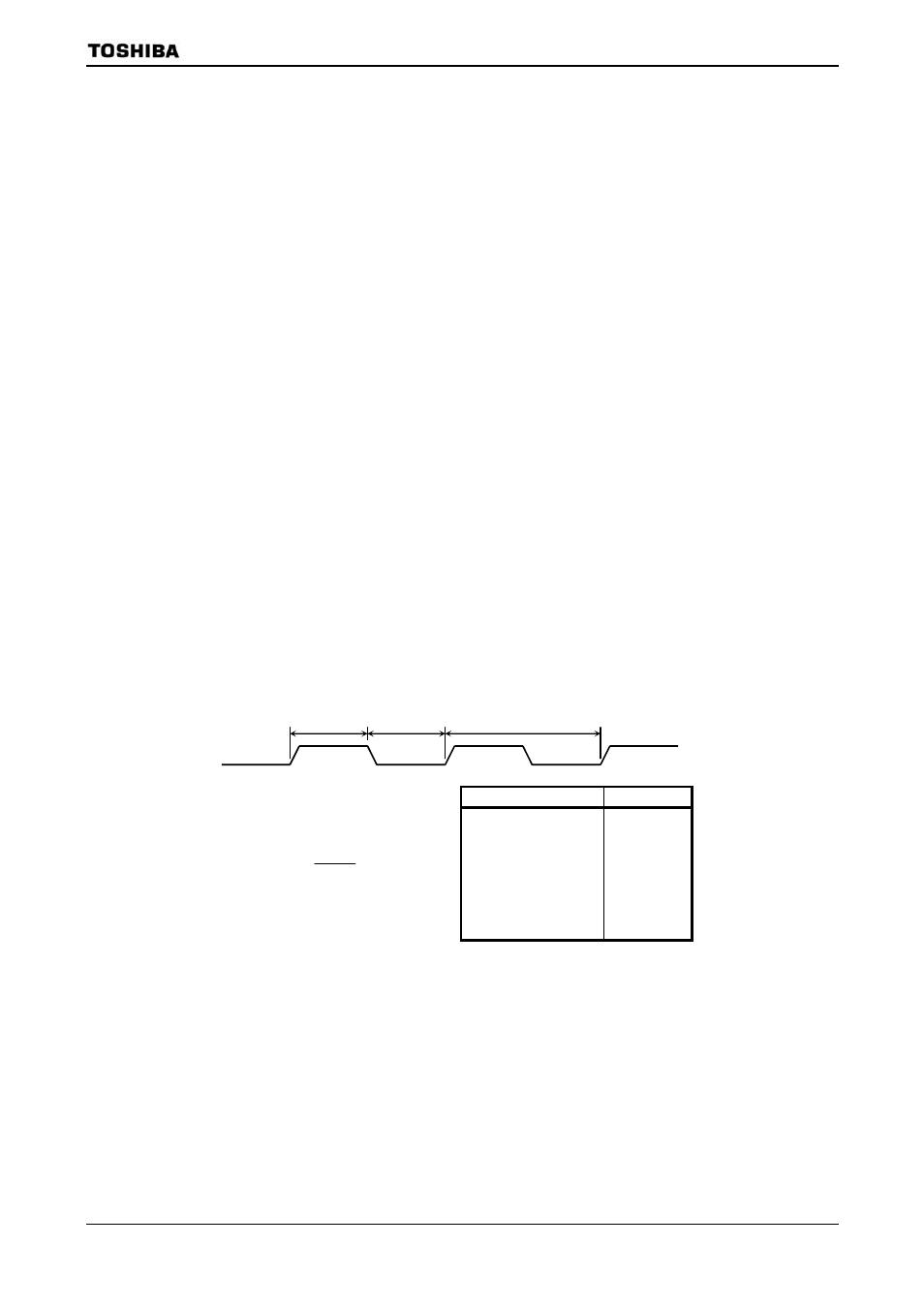

Figure 3.10.7 Clock Source

t

HIGH

t

LOW

1/fscl

t

LOW

= 2

n

− 1

/f

SBI

t

HIGH

= 2

n

− 1

/f

SBI

+ 8/f

SBI

fscl

= 1/(t

LOW

+ t

HIGH

)

f

SBI

2

n

+ 8

=