13 capability pointer register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 98

4−8

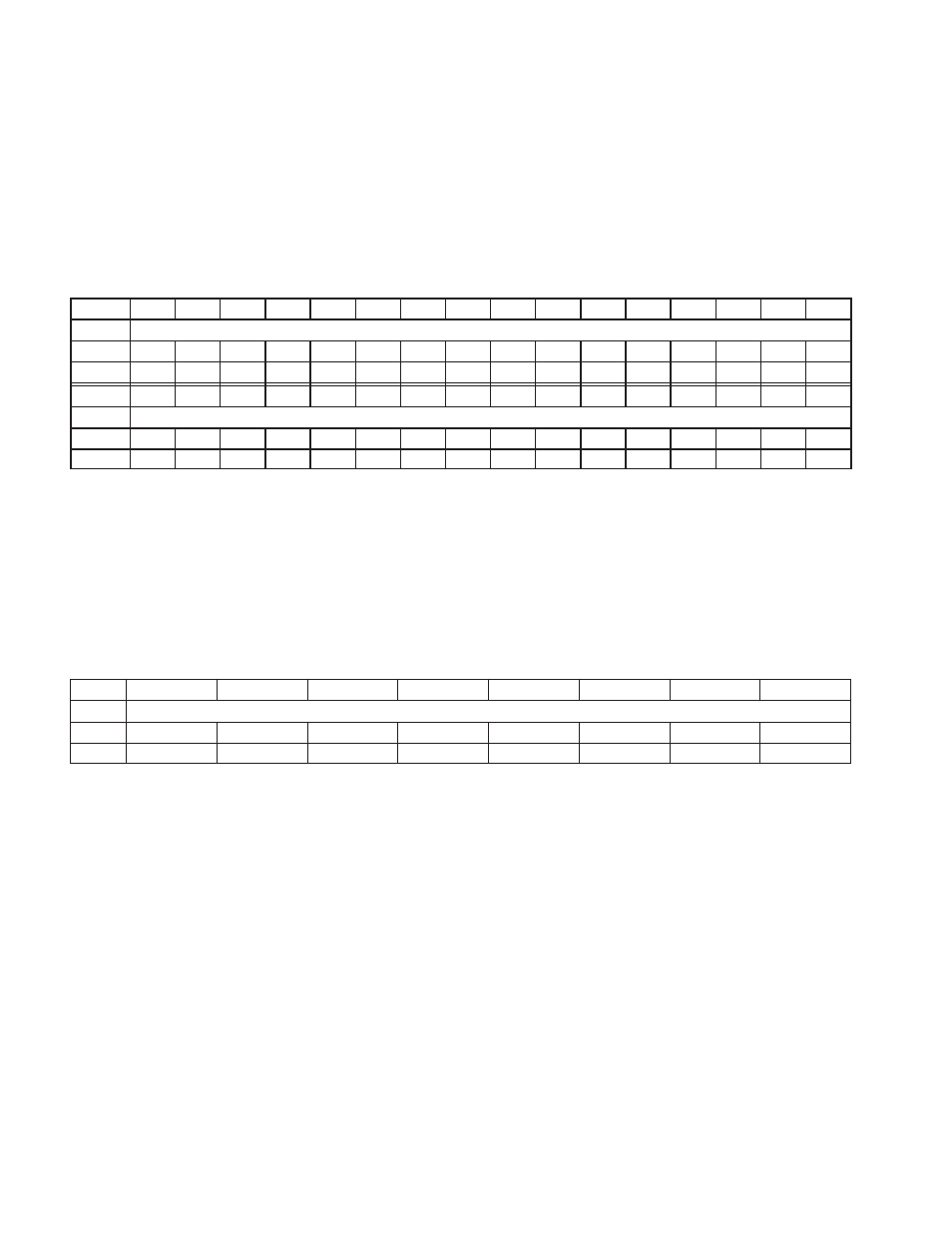

4.12 CardBus Socket Registers/ExCA Base Address Register

This register is programmed with a base address referencing the CardBus socket registers and the memory-mapped

ExCA register set. Bits 31−12 are read/write, and allow the base address to be located anywhere in the 32-bit PCI

memory address space on a 4-Kbyte boundary. Bits 11−0 are read-only, returning 0s when read. When software

writes all 1s to this register, the value read back is FFFF F000h, indicating that at least 4K bytes of memory address

space are required. The CardBus registers start at offset 000h, and the memory-mapped ExCA registers begin at

offset 800h. This register is not shared by functions 0 and 1, so the system maps each socket control register

separately.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

CardBus socket registers/ExCA base address

Type

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

CardBus socket registers/ExCA base address

Type

RW

RW

RW

RW

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

CardBus socket registers/ExCA base address

Offset:

10h

Type:

Read-only, Read/Write

Default: 0000

0000h

4.13 Capability Pointer Register

The capability pointer register provides a pointer into the PCI configuration header where the PCI power management

register block resides. PCI header doublewords at A0h and A4h provide the power management (PM) registers. Each

socket has its own capability pointer register. This register is read-only and returns A0h when read.

Bit

7

6

5

4

3

2

1

0

Name

Capability pointer

Type

R

R

R

R

R

R

R

R

Default

1

0

1

0

0

0

0

0

Register:

Capability pointer

Offset:

14h

Type:

Read-only

Default: A0h