7 header type and bist register, 8 smart card base address register 0 – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 278

13−6

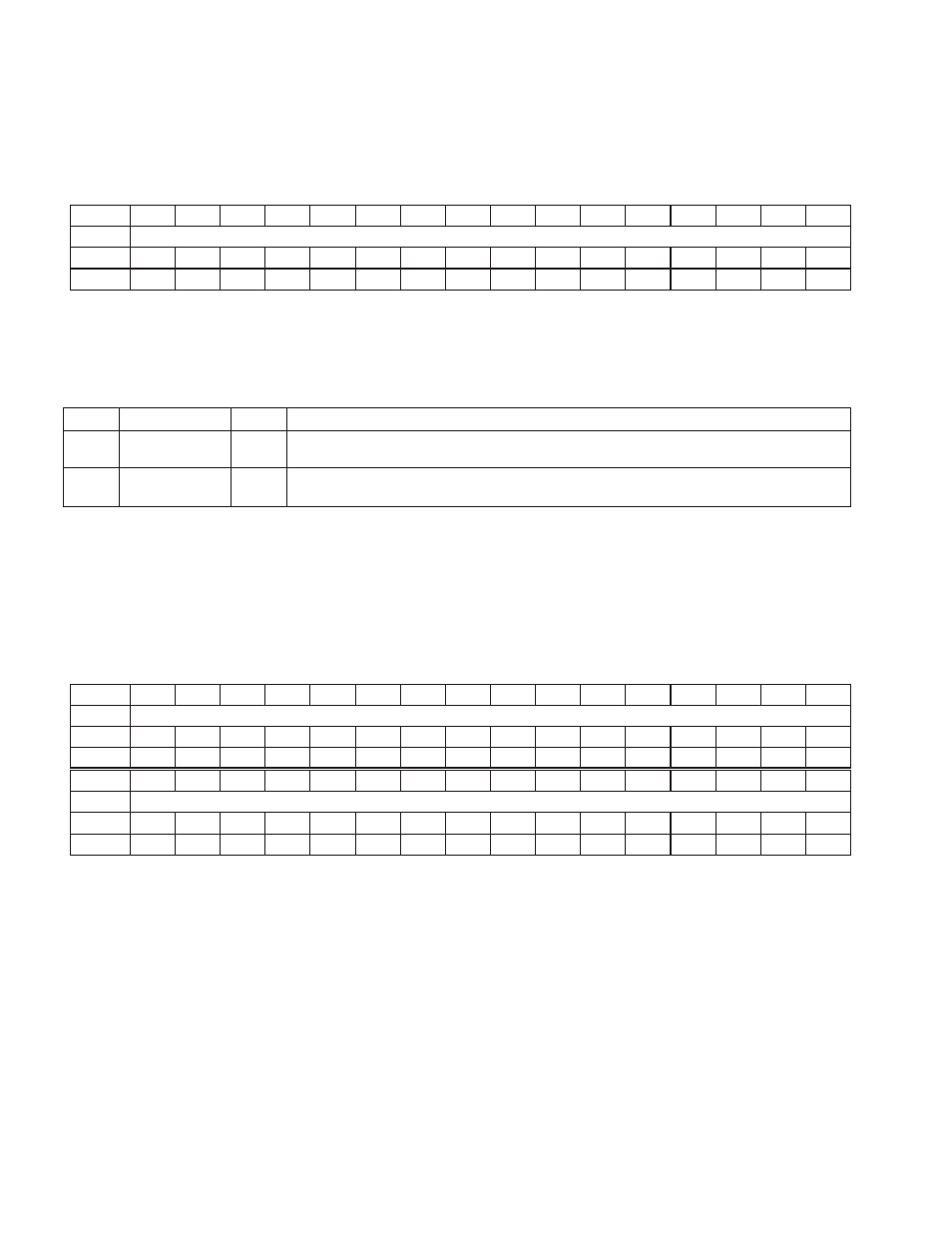

13.7 Header Type and BIST Register

The header type and built-in self-test (BIST) register indicates the Smart Card controller PCI header type and no

built-in self-test. See Table 13−6 for a complete description of the register contents.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Header type and BIST

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

Register:

Header type and BIST

Offset:

0Eh

Type:

Read-only

Default:

0080h

Table 13−6. Header Type and BIST Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

15−8

BIST

R

Built-in self-test. The Smart Card controller does not include a BIST; therefore, this field returns 00h

when read.

7−0

HEADER_TYPE

R

PCI header type. The Smart Card controller includes the standard PCI header. Bit 7 indicates if the Smart

Card is a multifunction device.

13.8 Smart Card Base Address Register 0

This register is used by this function to determine where to forward a memory transaction to the Smart Card global

control register set. Bits 31−12 of this register are read/write and allow the base address to be located anywhere in

the 32-bit PCI memory space on 4-Kbyte boundary. The window size is always 4K bytes. Bits 11−0 are read-only and

always return 0s. Write transactions to these bits have no effect. Bit 3 (0b) specifies that this window is

nonprefetchable. Bits 2−1 (00b) specify that this memory window can allocate anywhere in the 32-bit address space.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Smart Card base address register 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Smart Card base address register 0

Type

RW

RW

RW

RW

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Smart Card base address register 0

Offset:

10h

Type:

Read/Write, Read-only

Default:

0000 0000h