37 retry status register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 117

4−27

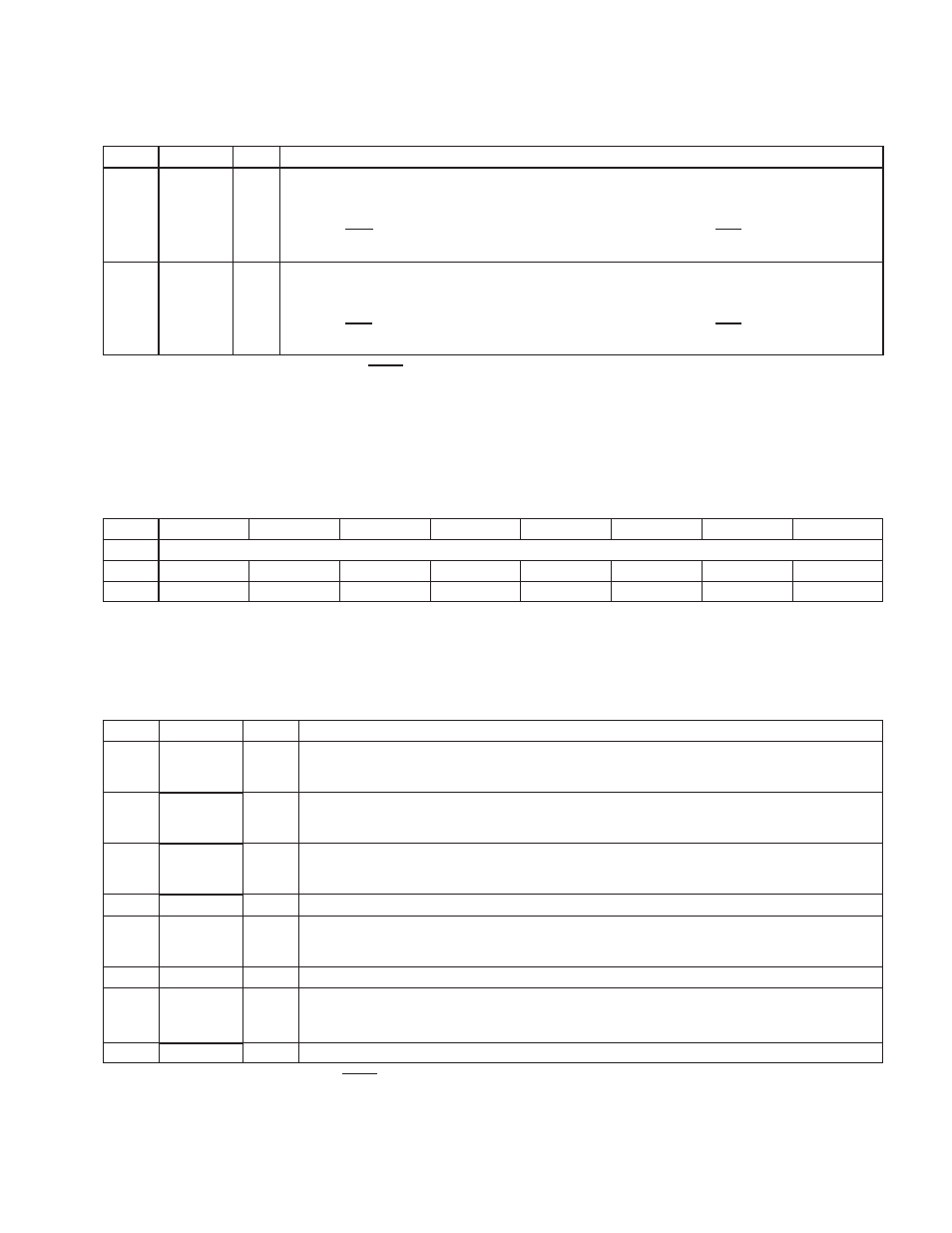

Table 4−14. Multifunction Routing Status Register Description (Continued)

BIT

SIGNAL

TYPE

FUNCTION

7−4 ‡

MFUNC1

RW

Multifunction terminal 1 configuration. These bits control the internal signal mapped to the MFUNC1 terminal

as follows:

0000 = GPI1

0100 = OHCI_LED 1000 = CAUDPWM

1100 = LEDA1

0001 = GPO1

0101 = IRQ5

1001 = IRQ9

1101 = LEDA2

0010 = INTB

0110 = RSVD

1010 = IRQ10

1110 = GPE

0011 = IRQ3

0111 = RSVD

1011 = IRQ11

1111 = IRQ15

3−0 ‡

MFUNC0

RW

Multifunction terminal 0 configuration. These bits control the internal signal mapped to the MFUNC0 terminal

as follows:

0000 = GPI0

0100 = IRQ4

1000 = CAUDPWM

1100 = LEDA1

0001 = GPO0

0101 = IRQ5

1001 = IRQ9

1101 = LEDA2

0010 = INTA

0110 = RSVD

1010 = IRQ10

1110 = GPE

0011 = IRQ3

0111 = RSVD

1011 = IRQ11

1111 = IRQ15

‡ These bits are cleared only by the assertion of GRST.

4.37 Retry Status Register

The contents of the retry status register enable the retry time-out counters and display the retry expiration status. The

flags are set when the PCI7x21/PCI7x11 controller, as a master, receives a retry and does not retry the request within

2

15

clock cycles. The flags are cleared by writing a 1 to the bit. Access this register only through function 0. See

Table 4−15 for a complete description of the register contents.

Bit

7

6

5

4

3

2

1

0

Name

Retry status

Type

RW

RW

RC

R

RC

R

RC

R

Default

1

1

0

0

0

0

0

0

Register:

Retry status

Offset:

90h (Functions 0, 1)

Type:

Read-only, Read/Write, Read/Clear

Default: C0h

Table 4−15. Retry Status Register Description

BIT

SIGNAL

TYPE

FUNCTION

7 ‡

PCIRETRY

RW

PCI retry time-out counter enable. This bit is encoded as:

0 = PCI retry counter disabled

1 = PCI retry counter enabled (default)

6 ‡§

CBRETRY

RW

CardBus retry time-out counter enable. This bit is encoded as:

0 = CardBus retry counter disabled

1 = CardBus retry counter enabled (default)

5 ‡

TEXP_CBB

RC

CardBus target B retry expired. Write a 1 to clear this bit.

0 = Inactive (default)

1 = Retry has expired.

4

RSVD

R

Reserved. This bit returns 0 when read.

3 ‡§

TEXP_CBA

RC

CardBus target A retry expired. Write a 1 to clear this bit.

0 = Inactive (default)

1 = Retry has expired.

2

RSVD

R

Reserved. This bit returns 0 when read.

1 ‡

TEXP_PCI

RC

PCI target retry expired. Write a 1 to clear this bit.

0 = Inactive (default)

1 = Retry has expired.

0

RSVD

R

Reserved. This bit returns 0 when read.

‡ This bit is cleared only by the assertion of GRST.

§ These bits are global in nature and must be accessed only through function 0.