5 timestamp offset register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 229

9−5

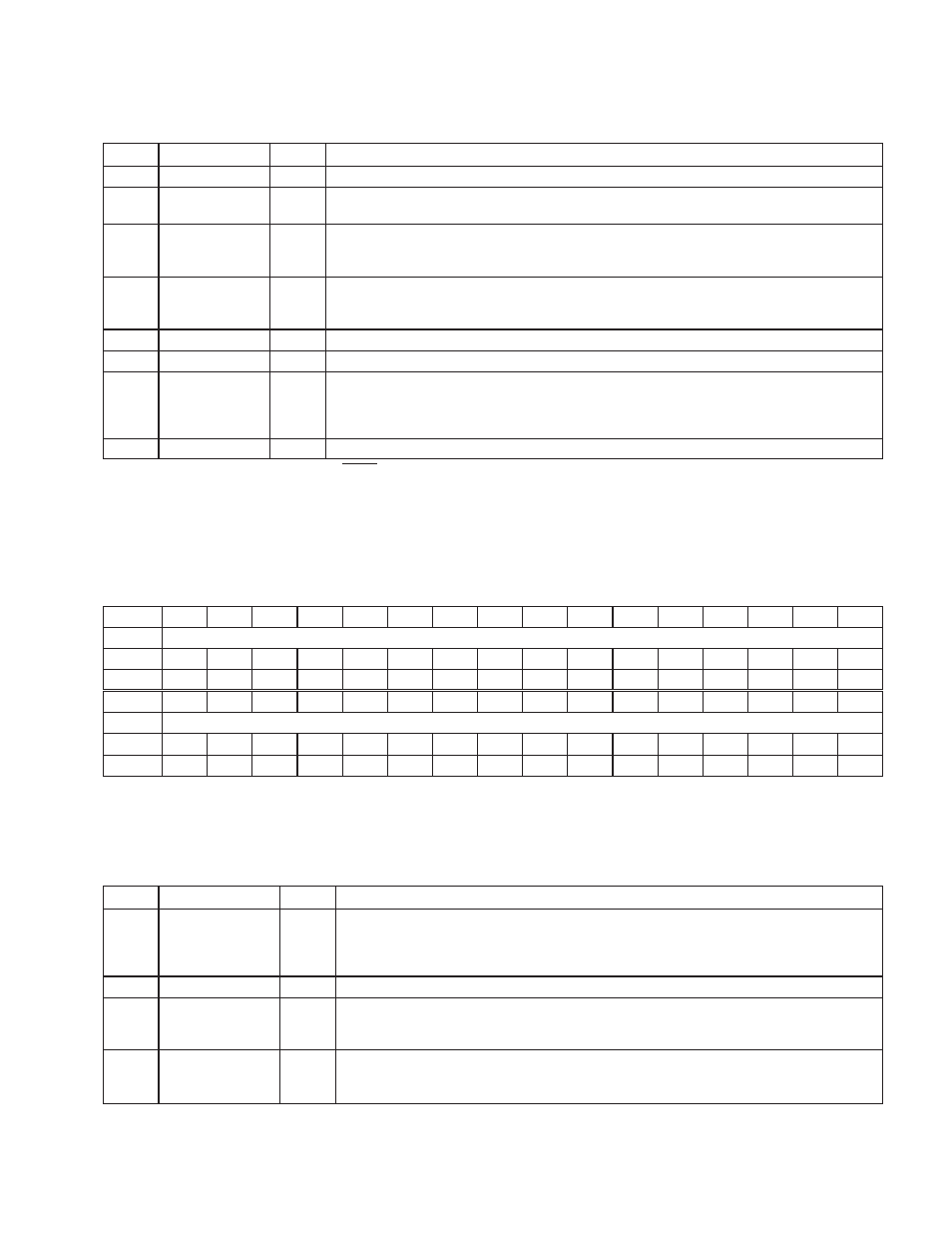

Table 9−3. Link Enhancement Register Description (Continued)

BIT

FIELD NAME

TYPE

DESCRIPTION

9

RSVD

R

Reserved. Bit 9 returns 0 when read.

8 ‡

enab_dv_ts

RW

Enable DV CIP timestamp enhancement. When bit 8 is set to 1, the enhancement is enabled for DV

CIP transmit streams (FMT = 00h). The default value for this bit is 0.

7 ‡

enab_unfair

RW

Enable asynchronous priority requests. OHCI-Lynx

compatible. Setting bit 7 to 1 enables the link to

respond to requests with priority arbitration. It is recommended that this bit be set to 1. The default value

for this bit is 0.

6

RSVD

R

This bit is not assigned in the PCI7x21/PCI7x11 follow-on products, because this bit location loaded

by the serial EEPROM from the enhancements field corresponds to bit 23 (programPhyEnable) in the

host controller control register at OHCI offset 50h/54h (see Section 8.16).

5−3

RSVD

R

Reserved. Bits 5−3 return 0s when read.

2 ‡

RSVD

R

Reserved. Bit 2 returns 0 when read.

1 ‡

enab_accel

RW

Enable acceleration enhancements. OHCI-Lynx

compatible. When bit 1 is set to 1, the PHY layer

is notified that the link supports the IEEE Std 1394a-2000 acceleration enhancements, that is,

ack-accelerated, fly-by concatenation, etc. It is recommended that this bit be set to 1. The default value

for this bit is 0.

0

RSVD

R

Reserved. Bit 0 returns 0 when read.

‡ This bit is cleared only by the assertion of GRST.

9.5

Timestamp Offset Register

The value of this register is added as an offset to the cycle timer value when using the MPEG, DV, and CIP

enhancements. A timestamp offset register is implemented per isochronous transmit context. The n value following

the offset indicates the context number (n = 0, 1, 2, 3,

…

, 7). These registers are programmed by software as

appropriate. See Table 9−4 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Timestamp offset

Type

RW

R

R

R

R

R

R

RW

RW

RW

RW

RW

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Timestamp offset

Type

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Timestamp offset

Offset:

A90h + (4*n)

Type:

Read/Write, Read-only

Default:

0000 0000h

Table 9−4. Timestamp Offset Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31

DisableInitialOffset

RW

Bit 31 disables the use of the initial timestamp offset when the MPEG2 enhancements are enabled.

A value of 0 indicates the use of the initial offset, a value of 1 indicates that the initial offset must not

be applied to the calculated timestamp. This bit has no meaning for the DV timestamp

enhancements. The default value for this bit is 0.

30−25

RSVD

R

Reserved. Bits 30−25 return 0s when read.

24−12

CycleCount

RW

This field adds an offset to the cycle count field in the timestamp when the DV or MPEG2

enhancements are enabled. The cycle count field is incremented modulo 8000; therefore, values in

this field must be limited between 0 and 7999. The default value for this field is all 0s.

11−0

CycleOffset

RW

This field adds an offset to the cycle offset field in the timestamp when the DV or MPEG2

enhancements are enabled. The cycle offset field is incremented modulo 3072; therefore, values in

this field must be limited between 0 and 3071. The default value for this field is all 0s.