Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 77

3−21

•

Ring indicate

•

PCI power management

•

Cardbus bridge power management

•

ACPI support

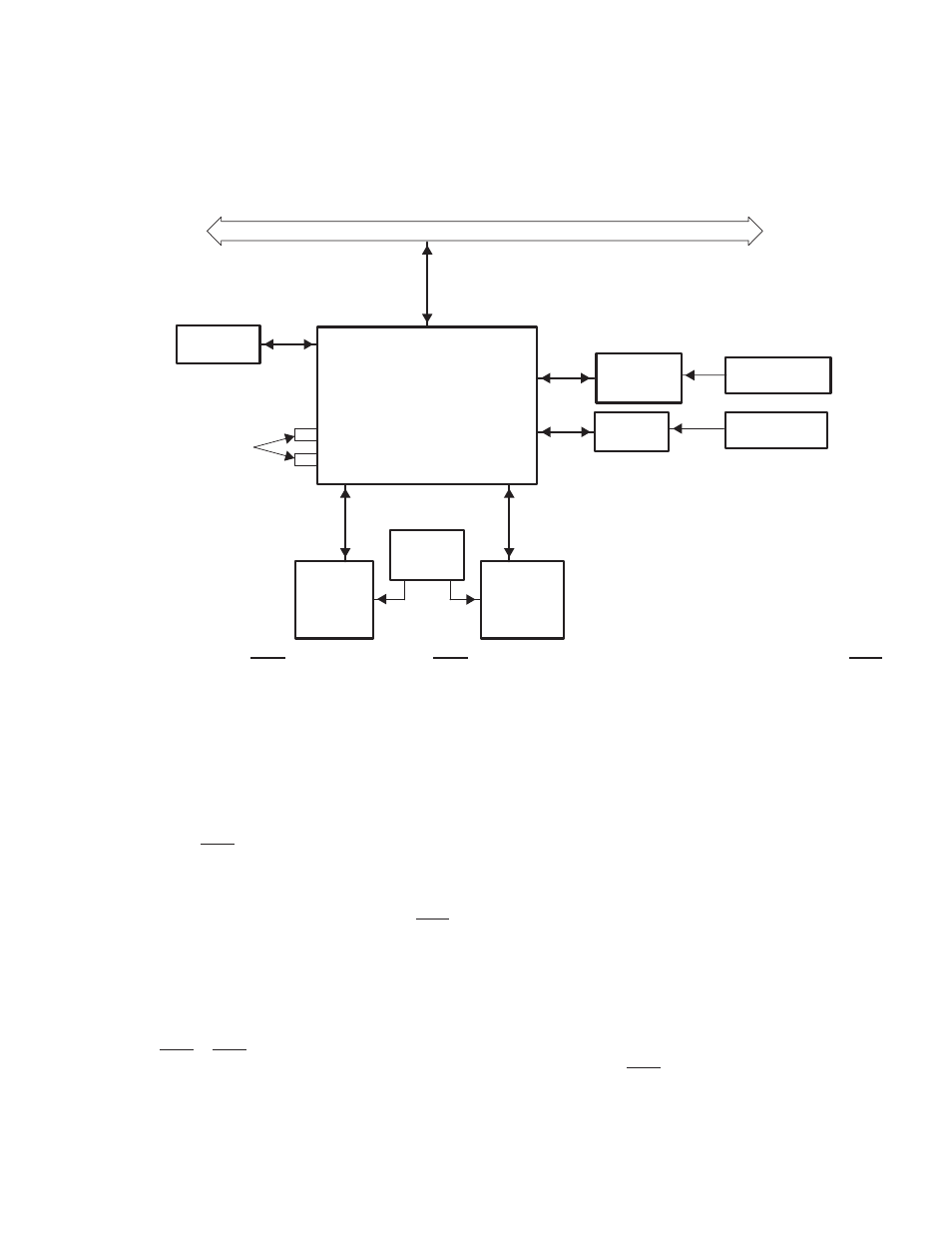

PCI Bus

PCI7x21/P

CI7x11

1394a

Socket

EEPROM

Power Switch

SD/MMC

PC

Card/

UltraMedia

Card

Power

Switch

PC

Card/

UltraMedia

Card

Power Switch

SD/MMC

MS/MSPRO

SM/xD

† The system connection to GRST is implementation-specific. GRST must be asserted on initial power up of the PCI7x21/PCI7x11 controller. PRST

must be asserted for subsequent warm resets.

Figure 3−13. System Diagram Implementing CardBus Device Class Power Management

3.8.1

1394 Power Management (Function 2)

The PCI7x21/PCI7x11 controller complies with PCI Bus Power Management Interface Specification. The controller

supports the D0 (uninitialized), D0 (active), D1, D2, and D3 power states as defined by the power-management

definition in the 1394 Open Host Controller Interface Specification, Appendix A.4 and PCI Bus Power Management

Specification. PME is supported to provide notification of wake events. Per Section A.4.2, the 1394 OHCI sets

PMCSR.PME_STS in the D0 state due to unmasked interrupt events. In previous OHCI implementations, unmasked

interrupt events were interpreted as (IntEvent.n && IntMask.n && IntMask.masterIntEnable), where n represents a

specific interrupt event. Based on feedback from Microsoft this implementation may cause problems with the existing

Windows power-management arcitecture as a PME and an interrupt could be simultaneously signaled on a transition

from the D1 to D0 state where interrupts were enabled to generate wake events. If bit 10

(ignore_mstrIntEna_for_pme) in the PCI miscellaneous configuration register (OHCI offset F0h, see Section 7.23)

is set, then the PCI7x21/PCI7x11 controller implements the preferred behavior as (IntEvent.n && IntMask.n).

Otherwise, the PCI7x21/PCI7x11 controller implements the preferred behavior as (IntEvent.n && IntMask.n &&

IntMask.masterIntEnable). In addition, when the ignore_mstrIntEna_for_pme bit is set, it causes bit 26 of the OHCI

vendor ID register (OHCI offset 40h, see Section 8.15) to read 1, otherwise, bit 26 reads 0. An open drain buffer is

used for PME. If PME is enabled in the power management control/status register (PCI offset A4h, see Section 4.44),

then insertion of a PC Card causes the PCI7x21/PCI7x11 controller to assert PME, which wakes the system from a

low power state (D3, D2, or D1). The OS services PME and takes the PCI7x21/PCI7x11 controller to the D0 state.