9 subsystem vendor identification register, 10 subsystem identification register, 11 capabilities pointer register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 245

11−7

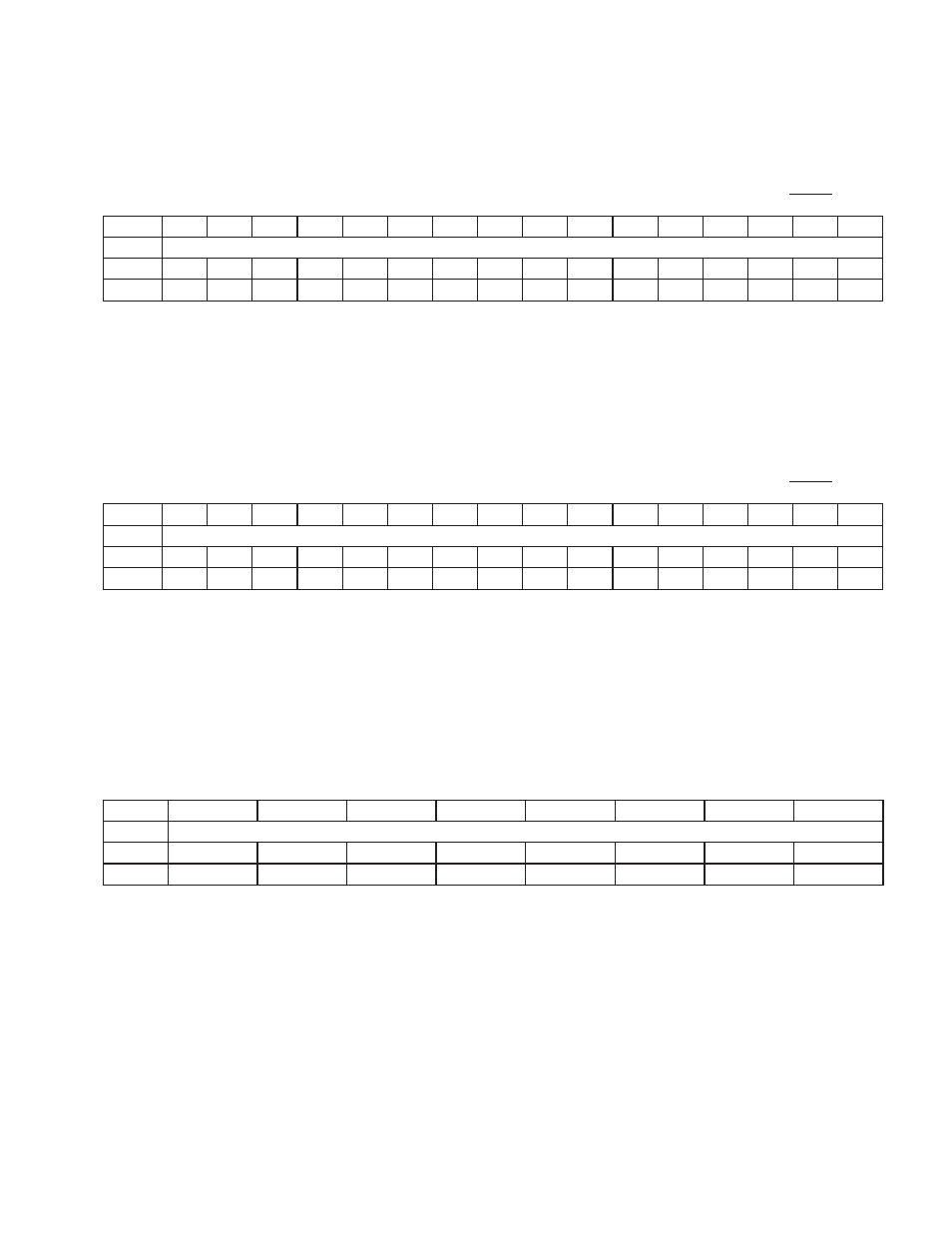

11.9 Subsystem Vendor Identification Register

The subsystem identification register, used for system and option card identification purposes, may be required for

certain operating systems. This read-only register is initialized through the EEPROM and can be written through the

subsystem access register at PCI offset 50h (see Section 11.22). All bits in this register are reset by GRST only.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Subsystem vendor identification

Type

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Subsystem vendor identification

Offset:

2Ch

Type:

Read/Update

Default:

0000h

11.10 Subsystem Identification Register

The subsystem identification register, used for system and option card identification purposes, may be required for

certain operating systems. This read-only register is initialized through the EEPROM and can be written through the

subsystem access register at PCI offset 50h (see Section 11.22). All bits in this register are reset by GRST only.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Subsystem identification

Type

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

RU

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Subsystem identification

Offset:

2Eh

Type:

Read/Update

Default:

0000h

11.11

Capabilities Pointer Register

The power management capabilities pointer register provides a pointer into the PCI configuration header where the

power-management register block resides. Since the PCI power management registers begin at 44h, this read-only

register is hardwired to 44h.

Bit

7

6

5

4

3

2

1

0

Name

Capabilities pointer

Type

R

R

R

R

R

R

R

R

Default

0

1

0

0

0

1

0

0

Register:

Capabilities pointer

Offset:

34h

Type:

Read-only

Default:

44h