6 switching characteristics for phy port interface – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 296

14−6

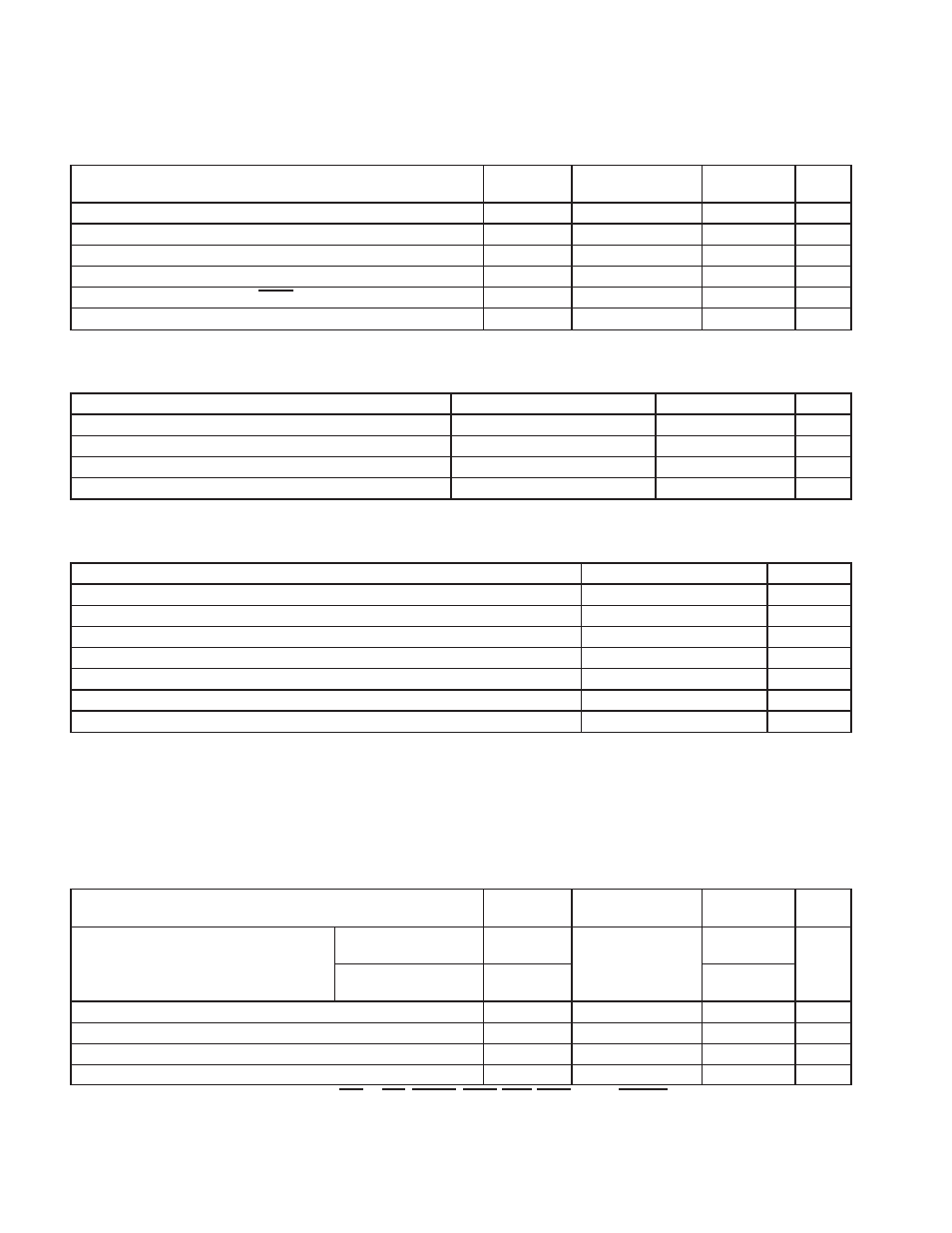

14.5 PCI Clock/Reset Timing Requirements Over Recommended Ranges of Supply

Voltage and Operating Free-Air Temperature

PARAMETER

ALTERNATE

SYMBOL

TEST CONDITIONS

MIN

MAX

UNIT

tc

Cycle time, PCLK

tcyc

30

ns

tw(H)

Pulse duration (width), PCLK high

thigh

11

ns

tw(L)

Pulse duration (width), PCLK low

tlow

11

ns

tr, tf

Slew rate, PCLK

∆

v/

∆

t

1

4

V/ns

tw

Pulse duration (width), GRST

trst

1

ms

tsu

Setup time, PCLK active at end of PRST

trst-clk

100

m

s

14.6 Switching Characteristics for PHY Port Interface

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Jitter, transmit

Between TPA and TPB

±

0.15

ns

Skew, transmit

Between TPA and TPB

±

0.10

ns

tr

TP differential rise time, transmit

10% to 90%, at 1394 connector

0.5

1.2

ns

tf

TP differential fall time, transmit

90% to 10%, at 1394 connector

0.5

1.2

ns

14.7 Operating, Timing, and Switching Characteristics of XI

PARAMETER

MIN

TYP

MAX

UNIT

VDD

3.0

3.3

3.6

V (PLLVCC)

VIH

High-level input voltage

0.63 VCC

V

VIL

Low-level input voltage

0.33 VCC

V

Input clock frequency

24.576

MHz

Input clock frequency tolerance

<100

PPM

Input slew rate

0.2

4

V/ns

Input clock duty cycle

40%

60%

14.8 PCI Timing Requirements Over Recommended Ranges of Supply Voltage and

Operating Free-Air Temperature

This data manual uses the following conventions to describe time ( t ) intervals. The format is t

A

, where subscript A

indicates the type of dynamic parameter being represented. One of the following is used: t

pd

= propagation delay time,

t

d

(t

en

, t

dis

) = delay time, t

su

= setup time, and t

h

= hold time.

PARAMETER

ALTERNATE

SYMBOL

TEST CONDITIONS

MIN

MAX

UNIT

tpd

Propagation delay time, See Note 4

PCLK-to-shared signal

valid delay time

tval

CL = 50 pF,

11

ns

tpd

Propagation delay time, See Note 4

PCLK-to-shared signal

invalid delay time

tinv

CL = 50 pF,

See Note 4

2

ns

ten

Enable time, high impedance-to-active delay time from PCLK

ton

2

ns

tdis

Disable time, active-to-high impedance delay time from PCLK

toff

28

ns

tsu

Setup time before PCLK valid

tsu

7

ns

th

Hold time after PCLK high

th

0

ns

NOTE 4: PCI shared signals are AD31−AD0, C/BE3−C/BE0, FRAME, TRDY, IRDY, STOP, IDSEL, DEVSEL, and PAR.