Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 131

5−3

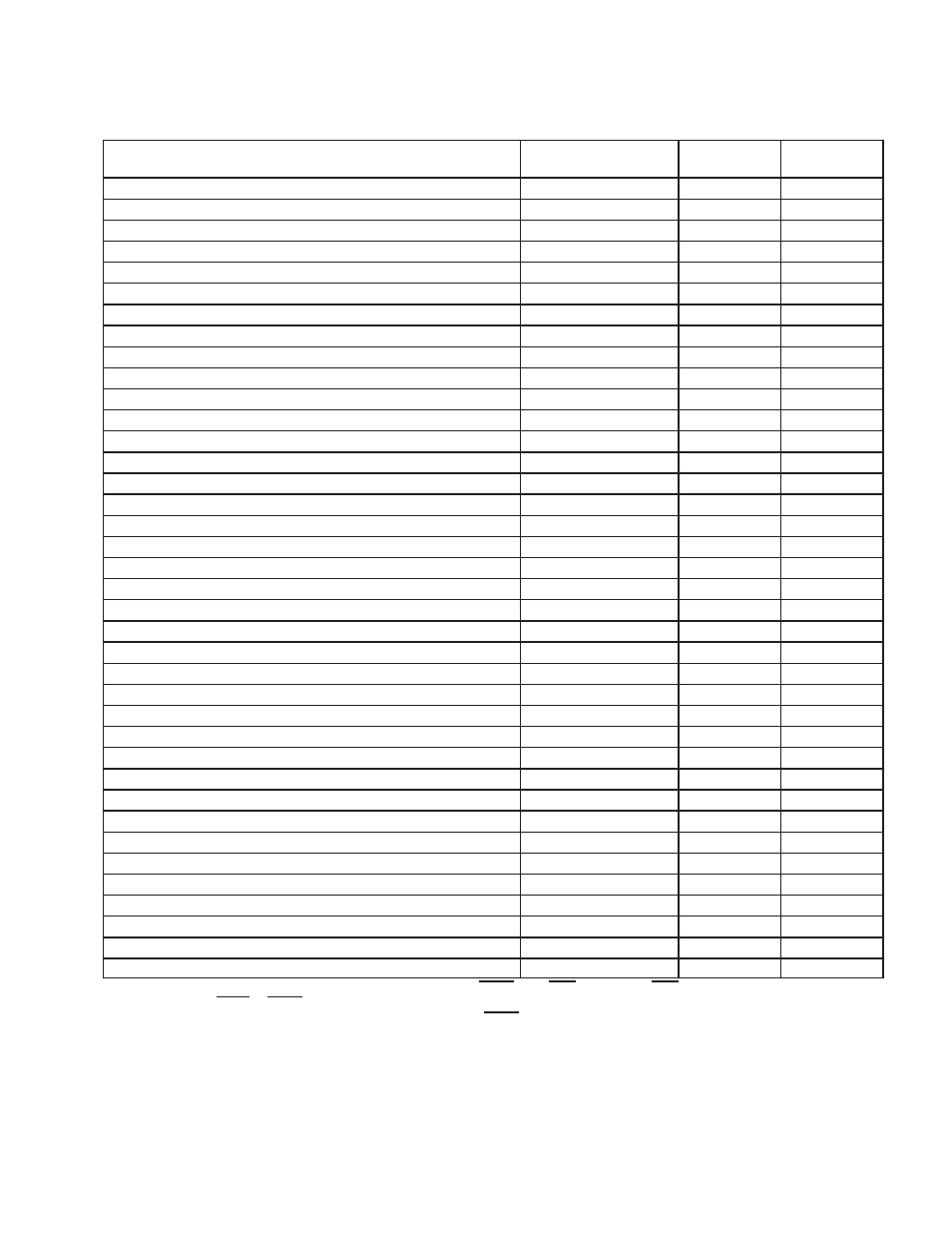

Table 5−1. ExCA Registers and Offsets

EXCA REGISTER NAME

PCI MEMORY ADDRESS

OFFSET (HEX)

EXCA OFFSET

(CARD A)

EXCA OFFSET

(CARD B)

Identification and revision ‡

800

00

40

Interface status

801

01

41

Power control †

802†

02

42

Interrupt and general control †

803†

03

43

Card status change †

804†

04

44

Card status change interrupt configuration †

805†

05

45

Address window enable

806

06

46

I / O window control

807

07

47

I / O window 0 start-address low-byte

808

08

48

I / O window 0 start-address high-byte

809

09

49

I / O window 0 end-address low-byte

80A

0A

4A

I / O window 0 end-address high-byte

80B

0B

4B

I / O window 1 start-address low-byte

80C

0C

4C

I / O window 1 start-address high-byte

80D

0D

4D

I / O window 1 end-address low-byte

80E

0E

4E

I / O window 1 end-address high-byte

80F

0F

4F

Memory window 0 start-address low-byte

810

10

50

Memory window 0 start-address high-byte

811

11

51

Memory window 0 end-address low-byte

812

12

52

Memory window 0 end-address high-byte

813

13

53

Memory window 0 offset-address low-byte

814

14

54

Memory window 0 offset-address high-byte

815

15

55

Card detect and general control †

816

16

56

Reserved

817

17

57

Memory window 1 start-address low-byte

818

18

58

Memory window 1 start-address high-byte

819

19

59

Memory window 1 end-address low-byte

81A

1A

5A

Memory window 1 end-address high-byte

81B

1B

5B

Memory window 1 offset-address low-byte

81C

1C

5C

Memory window 1 offset-address high-byte

81D

1D

5D

Global control ‡

81E

1E

5E

Reserved

81F

1F

5F

Memory window 2 start-address low-byte

820

20

60

Memory window 2 start-address high-byte

821

21

61

Memory window 2 end-address low-byte

822

22

62

Memory window 2 end-address high-byte

823

23

63

Memory window 2 offset-address low-byte

824

24

64

Memory window 2 offset-address high-byte

825

25

65

† One or more bits in this register are cleared only by the assertion of GRST when PME is enabled. If PME is not enabled, then this bit is cleared

by the assertion of PRST or GRST.

‡ One or more bits in this register are cleared only by the assertion of GRST.