7 programmable interrupt subsystem – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 72

3−16

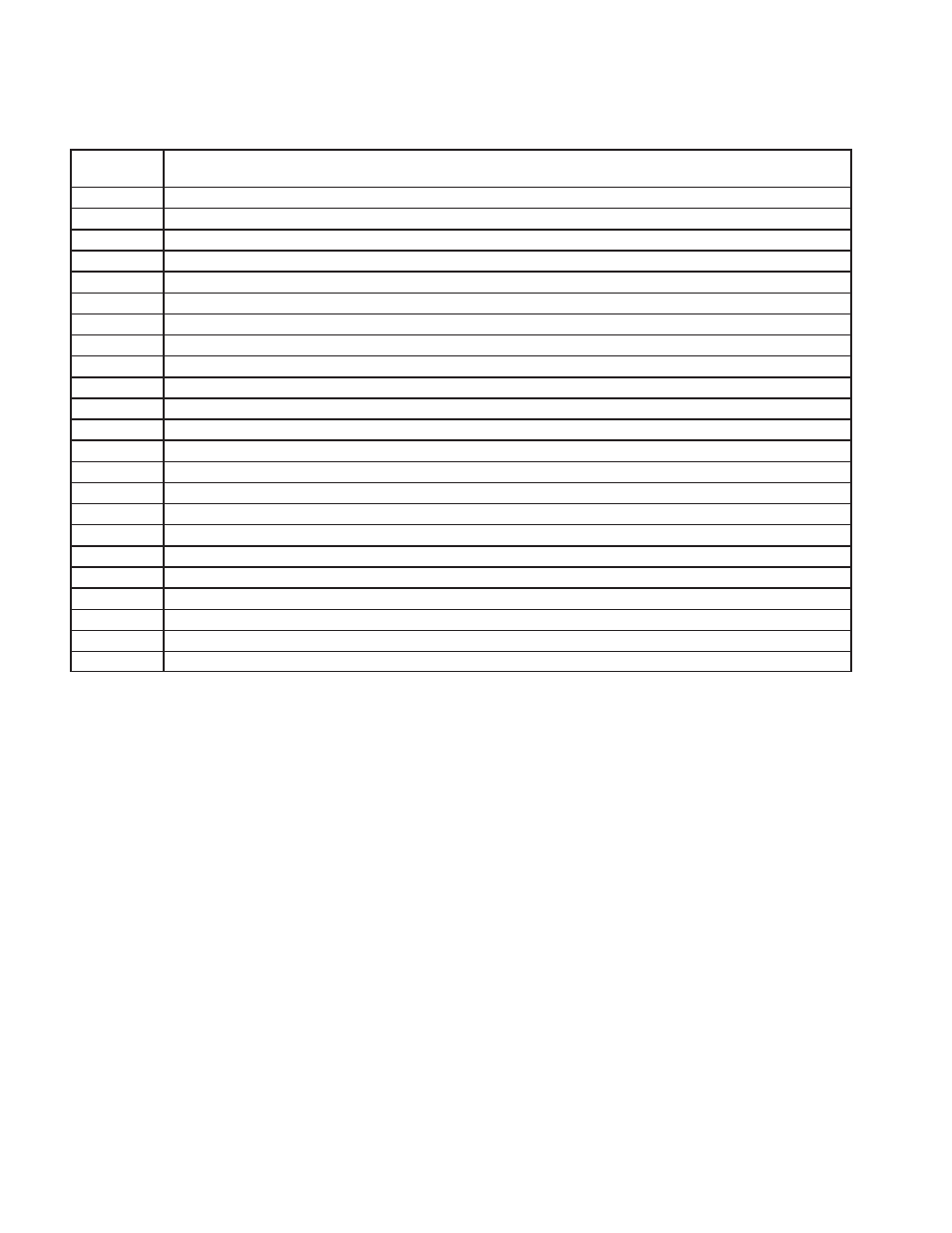

Table 3−9. EEPROM Loading Map (Continued)

SERIAL ROM

OFFSET

BYTE DESCRIPTION

49h

PCI 94h, slot 0 3.3 V maximum current

4Ah

PCI 98h, slot 1 3.3 V maximum current

4Bh

PCI 9Ch, slot 2 3.3 V maximum current

4Ch

Reserved (PCI A0h, slot 3 3.3 V maximum current)

4Dh

Reserved (PCI A4h, slot 4 3.3 V maximum current)

4Eh

Reserved (PCI A8h, slot 5 3.3 V maximum current)

4Fh

PCI Smart Card function indicator (05h)

50h

Number of bytes (0Eh)

51h

PCI 09h, class code, byte 0

52h

PCI 0Ah, class code, byte 1

53h

PCI 0Bh, class code, byte 2

54h

PCI 2Ch, subsystem vendor ID, byte 0

55h

PCI 2Dh, subsystem vendor ID, byte 1

56h

PCI 2Eh, subsystem ID, byte 0

57h

PCI 2Fh, subsystem ID, byte 1

58h

PCI 4Ch, general control bits 6−4

59h

PCI 58h, Smart Card configuration 1, byte 0, bits 6−4, 2−0

5Ah

PCI 59h, Smart Card configuration 1, byte 1, bits 6−4, 2−0

5Bh

PCI 5Ah, Smart Card configuration 1, byte 2, bits 6−4, 2−0

5Ch

PCI 5Bh, Smart Card configuration 1, byte 3, bits 7−4, 2−0

5Dh

PCI 5Ch, Smart Card configuration 2, byte 0

5Eh

PCI 5Dh, Smart Card configuration 2, byte 1

5Fh

End-of-list indicator (80h)

3.7

Programmable Interrupt Subsystem

Interrupts provide a way for I/O devices to let the microprocessor know that they require servicing. The dynamic

nature of PC Cards and the abundance of PC Card I/O applications require substantial interrupt support from the

PCI7x21/PCI7x11 controller. The PCI7x21/PCI7x11 controller provides several interrupt signaling schemes to

accommodate the needs of a variety of platforms. The different mechanisms for dealing with interrupts in this

controller are based on various specifications and industry standards. The ExCA register set provides interrupt

control for some 16-bit PC Card functions, and the CardBus socket register set provides interrupt control for the

CardBus PC Card functions. The PCI7x21/PCI7x11 controller is, therefore, backward compatible with existing

interrupt control register definitions, and new registers have been defined where required.

The PCI7x21/PCI7x11 controller detects PC Card interrupts and events at the PC Card interface and notifies the host

controller using one of several interrupt signaling protocols. To simplify the discussion of interrupts in the

PCI7x21/PCI7x11 controller, PC Card interrupts are classified either as card status change (CSC) or as functional

interrupts.

The method by which any type of PCI7x21/PCI7x11 interrupt is communicated to the host interrupt controller varies

from system to system. The PCI7x21/PCI7x11 controller offers system designers the choice of using parallel PCI

interrupt signaling, parallel ISA-type IRQ interrupt signaling, or the IRQSER serialized ISA and/or PCI interrupt

protocol. It is possible to use the parallel PCI interrupts in combination with either parallel IRQs or serialized IRQs,

as detailed in the sections that follow. All interrupt signaling is provided through the seven multifunction terminals,

MFUNC0−MFUNC6.