36 multifunction routing status register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 116

4−26

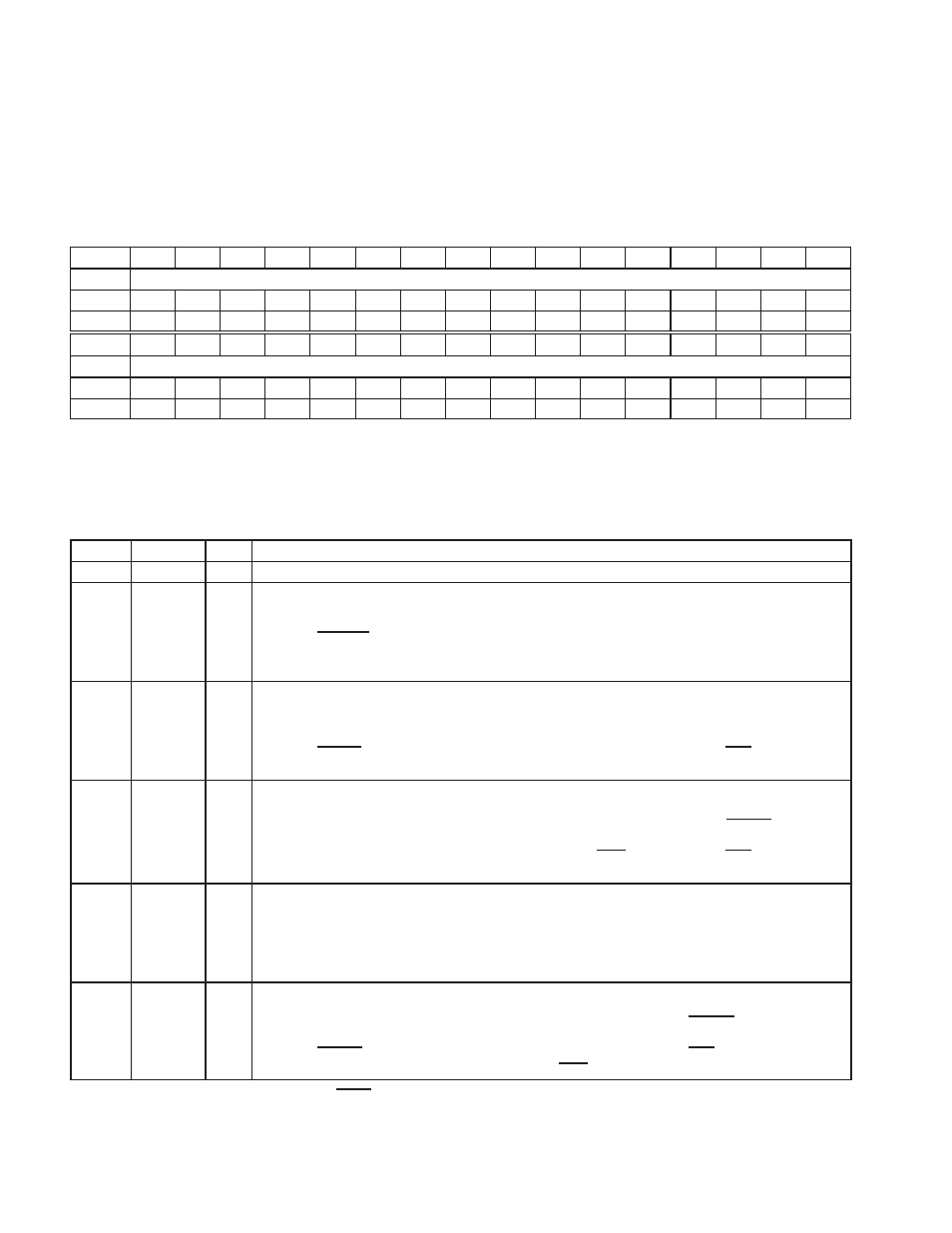

4.36 Multifunction Routing Status Register

The multifunction routing status register is used to configure the MFUNC6−MFUNC0 terminals. These terminals may

be configured for various functions. This register is intended to be programmed once at power-on initialization. The

default value for this register can also be loaded through a serial EEPROM. See Table 4−14 for a complete description

of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Multifunction routing status

Type

R

RW

RW

RW

R

RW

RW

RW

R

RW

RW

RW

R

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Multifunction routing status

Type

R

RW

RW

RW

R

RW

RW

RW

R

RW

RW

RW

R

RW

RW

RW

Default

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Multifunction routing status

Offset:

8Ch

Type:

Read/Write, Read-only

Default: 0000 1000h

Table 4−14. Multifunction Routing Status Register Description

BIT

SIGNAL

TYPE

FUNCTION

31−28 ‡

RSVD

R

Bits 31−28 return 0s when read.

27−24 ‡

MFUNC6

RW

Multifunction terminal 6 configuration. These bits control the internal signal mapped to the MFUNC6 terminal

as follows:

0000 = RSVD

0100 = IRQ4

1000 = IRQ8

1100 = IRQ12

0001 = CLKRUN

0101 = IRQ5

1001 = IRQ9

1101 = IRQ13

0010 = IRQ2

0110 = IRQ6

1010 = IRQ10

1110 = IRQ14

0011 = IRQ3

0111 = IRQ7

1011 = IRQ11

1111 = IRQ15

23−20 ‡

MFUNC5

RW

Multifunction terminal 5 configuration. These bits control the internal signal mapped to the MFUNC5 terminal

as follows:

0000 = GPI4

0100 = SC_DBG_RX

1000 = CAUDPWM

1100 = LEDA1

0001 = GPO4

0101 = IRQ5

1001 = IRQ9

1101 = LED_SKT

0010 = PCGNT

0110 = RSVD

1010 = FM_LED

1110 = GPE

0011 = IRQ3

0111 = RSVD

1011 = OHCI_LED

1111 = IRQ15

19−16 ‡

MFUNC4

RW

Multifunction terminal 4 configuration. These bits control the internal signal mapped to the MFUNC4 terminal

as follows:

0000 = GPI3

0100 = IRQ4

1000 = CAUDPWM

1100 = RI_OUT

0001 = GPO3

0101 = SC_DBG_TX

1001 = IRQ9

1101 = LED_SKT

0010 = RSVD

0110 = RSVD

1010 = INTD

1110 = GPE

0011 = IRQ3

0111 = RSVD

1011 = FM_LED

1111 = IRQ15

15−12 ‡

MFUNC3

RW

Multifunction terminal 3 configuration. These bits control the internal signal mapped to the MFUNC3 terminal

as follows:

0000 = RSVD

0100 = IRQ4

1000 = IRQ8

1100 = IRQ12

0001 = IRQSER

0101 = IRQ5

1001 = IRQ9

1101 = IRQ13

0010 = IRQ2

0110 = IRQ6

1010 = IRQ10

1110 = IRQ14

0011 = IRQ3

0111 = IRQ7

1011 = IRQ11

1111 = IRQ15

11−8 ‡

MFUNC2

RW

Multifunction terminal 2 configuration. These bits control the internal signal mapped to the MFUNC2 terminal

as follows:

0000 = GPI2

0100 = IRQ4

1000 = CAUDPWM

1100 = RI_OUT

0001 = GPO2

0101 = IRQ5

1001 = FM_LED

1101 = TEST_MUX

0010 = PCREQ

0110 = RSVD

1010 = IRQ10

1110 = GPE

0011 = IRQ3

0111 = RSVD

1011 = INTC

1111 = IRQ7

‡ These bits are cleared only by the assertion of GRST.