22 interrupt mask register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 200

8−20

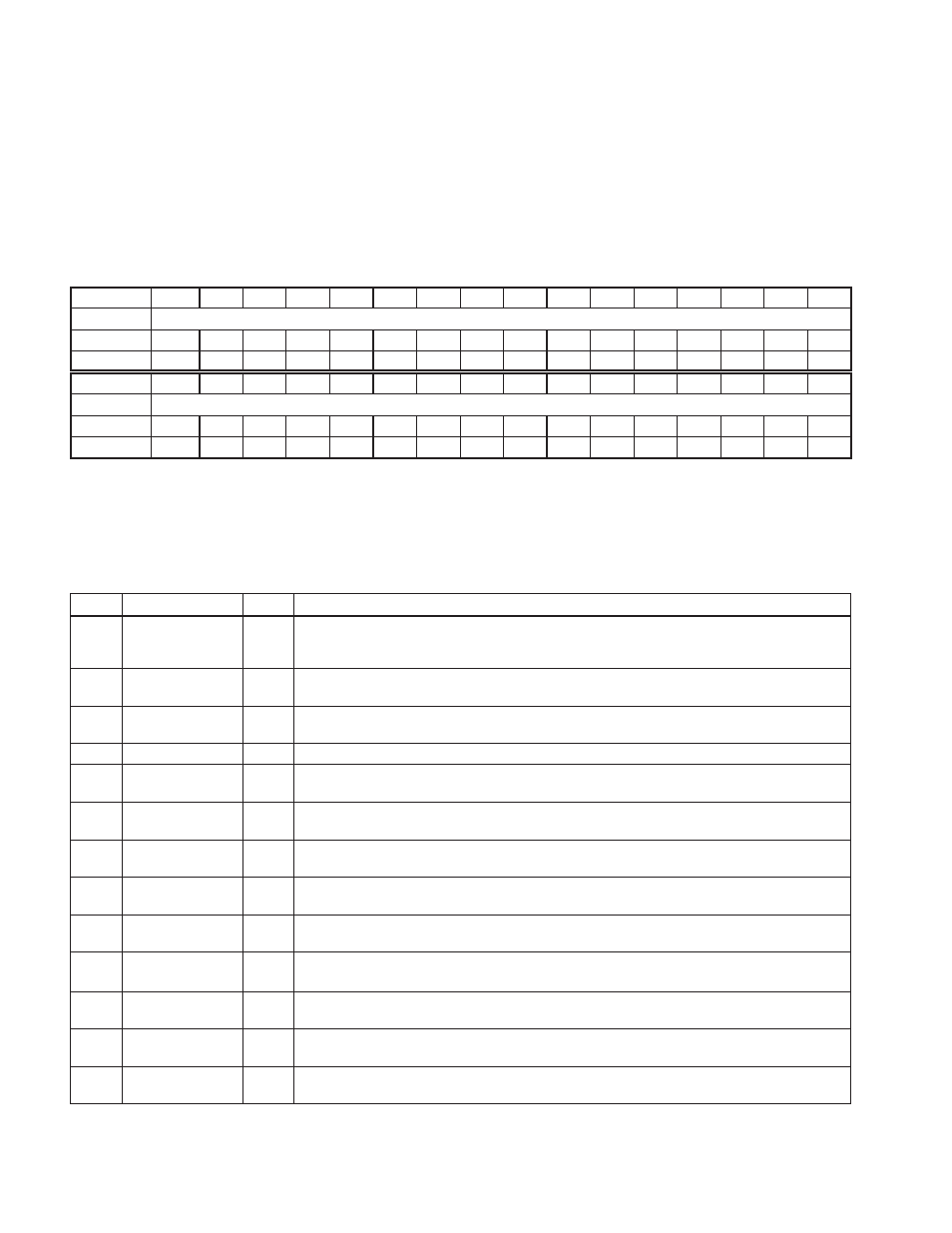

8.22 Interrupt Mask Register

The interrupt mask set/clear register enables the various PCI7x21/PCI7x11 interrupt sources. Reads from either the

set register or the clear register always return the contents of the interrupt mask register. In all cases except

masterIntEnable (bit 31) and vendorSpecific (bit 30), the enables for each interrupt event align with the interrupt event

register bits detailed in Table 8−15.

This register is fully compliant with the 1394 Open Host Controller Interface Specification and the PCI7x21/PCI7x11

controller adds an interrupt function to bit 30. See Table 8−16 for a complete description of bits 31 and 30.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Interrupt mask

Type

RSCU

RSC

RSC

R

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

Default

X

X

0

0

0

X

X

X

X

X

X

X

X

0

X

X

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Interrupt mask

Type

RSC

R

R

R

R

R

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

RSC

Default

0

0

0

0

0

0

X

X

X

X

X

X

X

X

X

X

Register:

Interrupt mask

Offset:

88h

set register

8Ch

clear register

Type:

Read/Set/Clear/Update, Read/Set/Clear, Read/Update, Read-only

Default:

XXXX 0XXXh

Table 8−16. Interrupt Mask Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31

masterIntEnable

RSCU

Master interrupt enable. If bit 31 is set to 1, then external interrupts are generated in accordance with

the interrupt mask register. If this bit is cleared, then external interrupts are not generated regardless

of the interrupt mask register settings.

30

VendorSpecific

RSC

When this bit and bit 30 (vendorSpecific) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this vendor-specific interrupt mask enables interrupt generation.

29

SoftInterrupt

RSC

When this bit and bit 29 (SoftInterrupt) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this soft-interrupt mask enables interrupt generation.

28

RSVD

R

Reserved. Bit 28 returns 0 when read.

27

ack_tardy

RSC

When this bit and bit 27 (ack_tardy) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this acknowledge-tardy interrupt mask enables interrupt generation.

26

phyRegRcvd

RSC

When this bit and bit 26 (phyRegRcvd) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this PHY-register interrupt mask enables interrupt generation.

25

cycleTooLong

RSC

When this bit and bit 25 (cycleTooLong) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this cycle-too-long interrupt mask enables interrupt generation.

24

unrecoverableError

RSC

When this bit and bit 24 (unrecoverableError) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this unrecoverable-error interrupt mask enables interrupt generation.

23

cycleInconsistent

RSC

When this bit and bit 23 (cycleInconsistent) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this inconsistent-cycle interrupt mask enables interrupt generation.

22

cycleLost

RSC

When this bit and bit 22 (cycleLost) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this lost-cycle interrupt mask enables interrupt generation.

21

cycle64Seconds

RSC

When this bit and bit 21 (cycle64Seconds) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this 64-second-cycle interrupt mask enables interrupt generation.

20

cycleSynch

RSC

When this bit and bit 20 (cycleSynch) in the interrupt event register at OHCI offset 80h/84h (see

Section 8.21) are set to 1, this isochronous-cycle interrupt mask enables interrupt generation.

19

phy

RSC

When this bit and bit 19 (phy) in the interrupt event register at OHCI offset 80h/84h (see Section 8.21)

are set to 1, this PHY-status-transfer interrupt mask enables interrupt generation.