Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 78

3−22

3.8.2

Integrated Low-Dropout Voltage Regulator (LDO-VR)

The PCI7x21/PCI7x11 controller requires 1.5-V core voltage. The core power can be supplied by the

PCI7x21/PCI7x11 controller itself using the internal

LDO-VR. The core power can alternatively be supplied by an

external power supply through the VR_PORT terminal. Table 3−14 lists the requirements for both the internal core

power supply and the external core power supply.

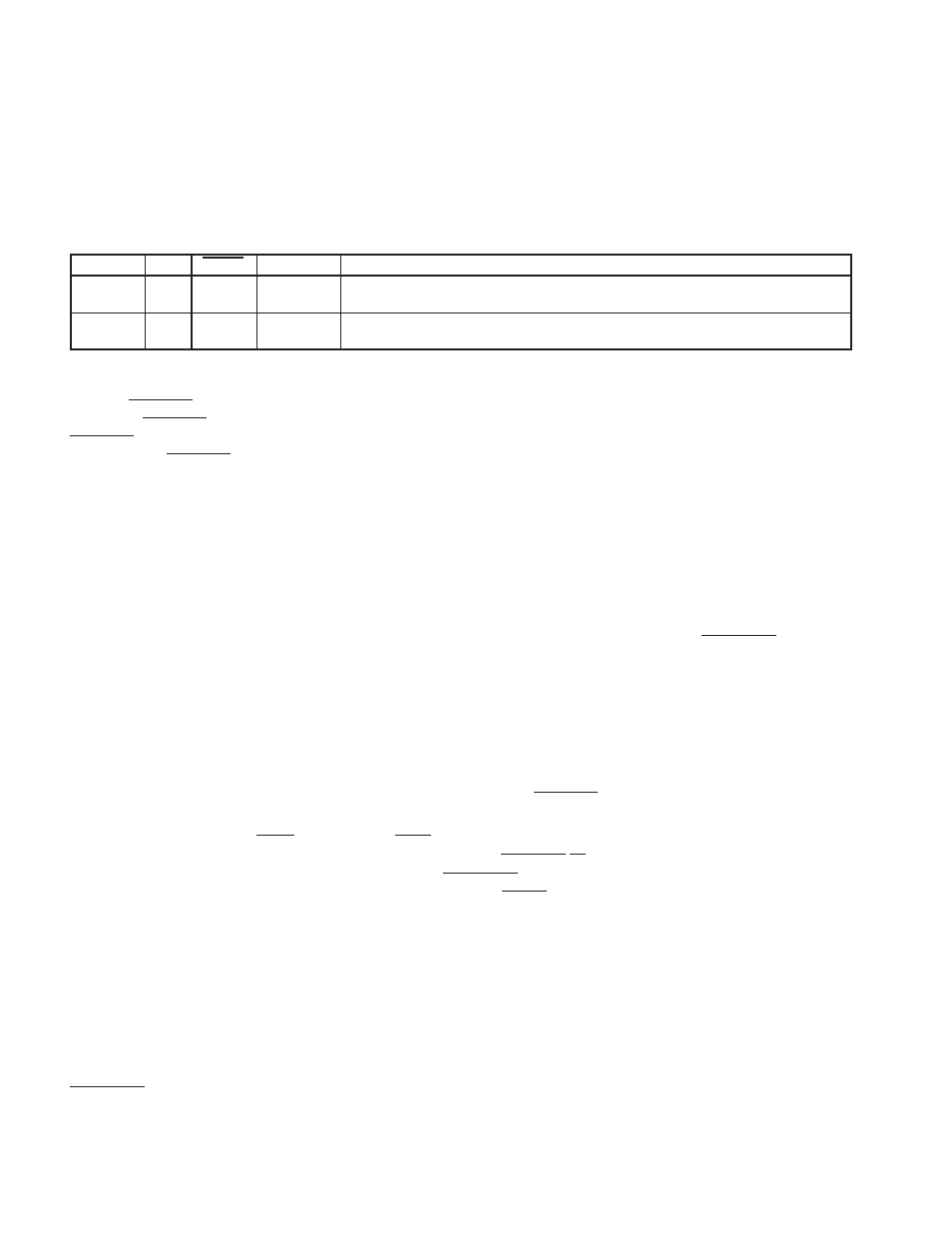

Table 3−14. Requirements for Internal/External 1.5-V Core Power Supply

SUPPLY

VCC

VR_EN

VR_PORT

NOTE

Internal

3.3 V

GND

1.5-V output

Internal 1.5-V LDO-VR is enabled. A 1.0-

µ

F bypass capacitor is required on the VR_PORT

terminal for decoupling. This output is not for external use.

External

3.3 V

VCC

1.5-V input

Internal 1.5-V LDO-VR is disabled. An external 1.5-V power supply, of minimum 50-mA

capacity, is required. A 0.1-

µ

F bypass capacitor on the VR_PORT terminal is required.

3.8.3

CardBus (Functions 0 and 1) Clock Run Protocol

The PCI CLKRUN feature is the primary method of power management on the PCI interface of the PCI7x21/PCI7x11

controller. CLKRUN signaling is provided through the MFUNC6 terminal. Since some chip sets do not implement

CLKRUN, this is not always available to the system designer, and alternate power-saving features are provided. For

details on the CLKRUN protocol see the PCI Mobile Design Guide.

The PCI7x21/PCI7x11 controller does not permit the central resource to stop the PCI clock under any of the following

conditions:

•

Bit 1 (KEEPCLK) in the system control register (PCI offset 80h, see Section 4.29) is set.

•

The 16-bit PC Card resource manager is busy.

•

The PCI7x21/PCI7x11 CardBus master state machine is busy. A cycle may be in progress on CardBus.

•

The PCI7x21/PCI7x11 master is busy. There may be posted data from CardBus to PCI in the

PCI7x21/PCI7x11 controller.

•

Interrupts are pending.

•

The CardBus CCLK for the socket has not been stopped by the PCI7x21/PCI7x11 CCLKRUN manager.

•

Bit 0 (KEEP_PCLK) in the miscellaneous configuration register (PCI offset F0h, see Section 7.23) is set.

•

The 1394 resource manager is busy.

•

The PCI7x21/PCI7x11 1394 master state machine is busy. A cycle may be in progress on 1394.

•

The PCI7x21/PCI7x11 master is busy. There may be posted data from the 1394 bus to PCI in the

PCI7x21/PCI7x11 controller.

•

PC Card interrogation is in progress.

•

The 1394 bus is not idle.

The PCI7x21/PCI7x11 controller restarts the PCI clock using the CLKRUN protocol under any of the following

conditions:

•

A 16-bit PC Card IREQ or a CardBus CINT has been asserted by either card.

•

A CardBus CBWAKE (CSTSCHG) or 16-bit PC Card STSCHG/RI event occurs in the socket.

•

A CardBus attempts to start the CCLK using CCLKRUN.

•

A CardBus card arbitrates for the CardBus bus using CREQ.

•

A 1394 device changes the status of the twisted pair lines from idle to active.

•

Bit 1 (KEEPCLK) in the system control register (PCI offset 80h, see Section 4.29) is set.

•

Data is in any of the FIFOs (receive or transmit).

•

The master state machine is busy.

•

There are pending interrupts.

3.8.4

CardBus PC Card Power Management

The PCI7x21/PCI7x11 controller implements its own card power-management engine that can turn off the CCLK to

a socket when there is no activity to the CardBus PC Card. The PCI clock-run protocol is followed on the CardBus

CCLKRUN interface to control this clock management.