25 isochronous receive interrupt event register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 204

8−24

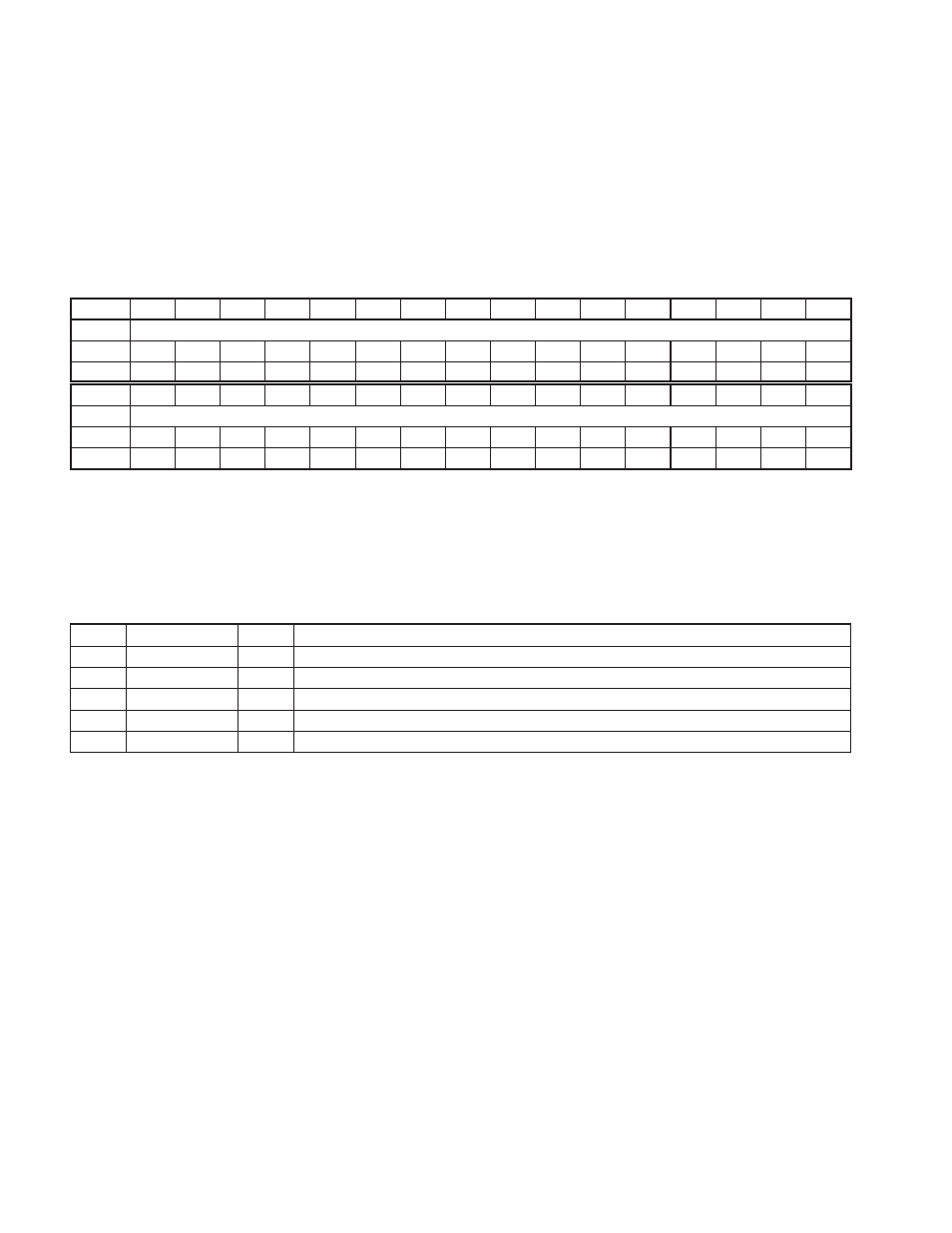

8.25 Isochronous Receive Interrupt Event Register

The isochronous receive interrupt event set/clear register reflects the interrupt state of the isochronous receive

contexts. An interrupt is generated on behalf of an isochronous receive context if an INPUT_* command completes

and its interrupt bits are set to 1. Upon determining that the isochRx (bit 7) interrupt in the interrupt event register at

OHCI offset 80h/84h (see Section 8.21) has occurred, software can check this register to determine which context(s)

caused the interrupt. The interrupt bits are set to 1 by an asserting edge of the corresponding interrupt signal or by

writing a 1 in the corresponding bit in the set register. The only mechanism to clear a bit in this register is to write a

1 to the corresponding bit in the clear register. See Table 8−18 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Isochronous receive interrupt event

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Isochronous receive interrupt event

Type

R

R

R

R

R

R

R

R

R

R

R

R

RSC

RSC

RSC

RSC

Default

0

0

0

0

0

0

0

0

0

0

0

0

X

X

X

X

Register:

Isochronous receive interrupt event

Offset:

A0h

set register

A4h

clear register [returns the contents of isochronous receive interrupt event register

bit-wise ANDed with the isochronous receive mask register when read]

Type:

Read/Set/Clear, Read-only

Default:

0000 000Xh

Table 8−18. Isochronous Receive Interrupt Event Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31−4

RSVD

R

Reserved. Bits 31−4 return 0s when read.

3

isoRecv3

RSC

Isochronous receive channel 3 caused the interrupt event register bit 7 (isochRx) interrupt.

2

isoRecv2

RSC

Isochronous receive channel 2 caused the interrupt event register bit 7 (isochRx) interrupt.

1

isoRecv1

RSC

Isochronous receive channel 1 caused the interrupt event register bit 7 (isochRx) interrupt.

0

isoRecv0

RSC

Isochronous receive channel 0 caused the interrupt event register bit 7 (isochRx) interrupt.