3 exca power control register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 135

5−7

5.3

ExCA Power Control Register

This register provides PC Card power control. Bit 7 of this register enables the 16-bit outputs on the socket interface,

and can be used for power management in 16-bit PC Card applications. See Table 5−5 for a complete description

of the register contents.

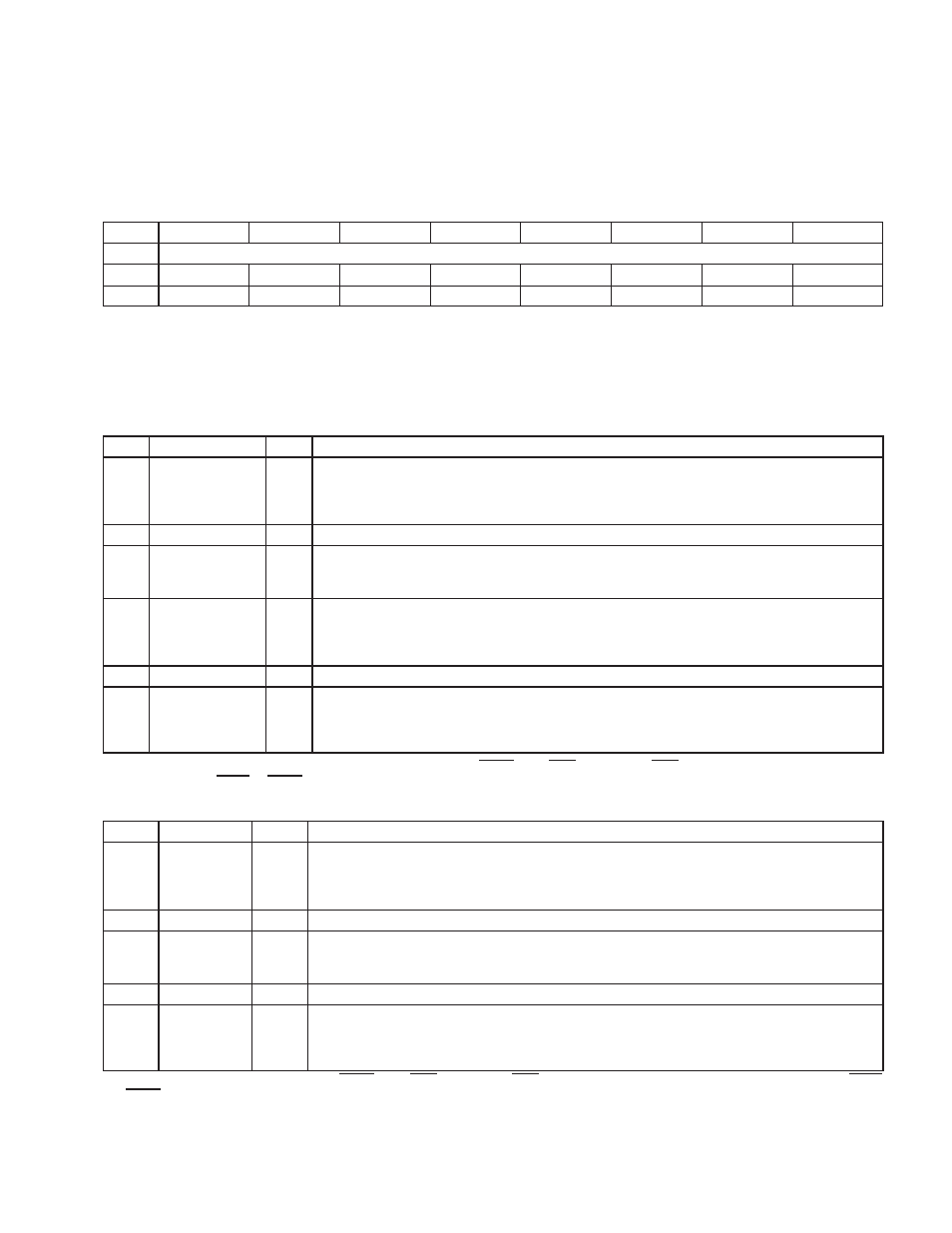

Bit

7

6

5

4

3

2

1

0

Name

ExCA power control

Type

RW

R

R

RW

RW

R

RW

RW

Default

0

0

0

0

0

0

0

0

Register:

ExCA power control

Offset:

CardBus Socket Address + 802h:

Card A ExCA Offset 02h

Card B ExCA Offset 42h

Type:

Read-only, Read/Write

Default: 00h

Table 5−4. ExCA Power Control Register Description—82365SL Support

BIT

SIGNAL

TYPE

FUNCTION

7

COE

RW

Card output enable. Bit 7 controls the state of all of the 16-bit outputs on the PCI7x21/PCI7x11 controller.

This bit is encoded as:

0 = 16-bit PC Card outputs disabled (default)

1 = 16-bit PC Card outputs enabled

6

RSVD

R

Reserved. Bit 6 returns 0 when read.

5 †

AUTOPWRSWEN

RW

Auto power switch enable.

0 = Automatic socket power switching based on card detects is disabled.

1 = Automatic socket power switching based on card detects is enabled.

4

CAPWREN

RW

PC Card power enable.

0 = VCC = No connection

1 = VCC is enabled and controlled by bit 2 (EXCAPOWER) of the system control register

(PCI offset 80h, see Section 4.29).

3−2

RSVD

R

Reserved. Bits 3 and 2 return 0s when read.

1−0

EXCAVPP

RW

PC Card VPP power control. Bits 1 and 0 are used to request changes to card VPP. The PCI7x21/PCI7x11

controller ignores this field unless VCC to the socket is enabled. This field is encoded as:

00 = No connection (default)

10 = 12 V

01 = VCC

11 = Reserved

† One or more bits in this register are cleared only by the assertion of GRST when PME is enabled. If PME is not enabled, then this bit is cleared

by the assertion of PRST or GRST.

Table 5−5. ExCA Power Control Register Description—82365SL-DF Support

BIT

SIGNAL

TYPE

FUNCTION

7 †

COE

RW

Card output enable. This bit controls the state of all of the 16-bit outputs on the PCI7x21/PCI7x11 controller.

This bit is encoded as:

0 = 16-bit PC Card outputs are disabled (default).

1 = 16-bit PC Card outputs are enabled.

6−5

RSVD

R

Reserved. These bits return 0s when read. Writes have no effect.

4−3 †

EXCAVCC

RW

VCC. These bits are used to request changes to card VCC. This field is encoded as:

00 = 0 V (default)

10 = 5 V

01 = 0 V reserved

11 = 3.3 V

2

RSVD

R

This bit returns 0 when read. A write has no effect.

1−0 †

EXCAVPP

RW

VPP. These bits are used to request changes to card VPP. The PCI7x21/PCI7x11 controller ignores this

field unless VCC to the socket is enabled (i.e., 5 Vdc or 3.3 Vdc). This field is encoded as:

00 = 0 V (default)

10 = 12 V

01 = VCC

11 = 0 V reserved

† This bit is cleared only by the assertion of GRST when PME is enabled. If PME is not enabled, then this bit is cleared by the assertion of PRST

or GRST.