Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 70

3−14

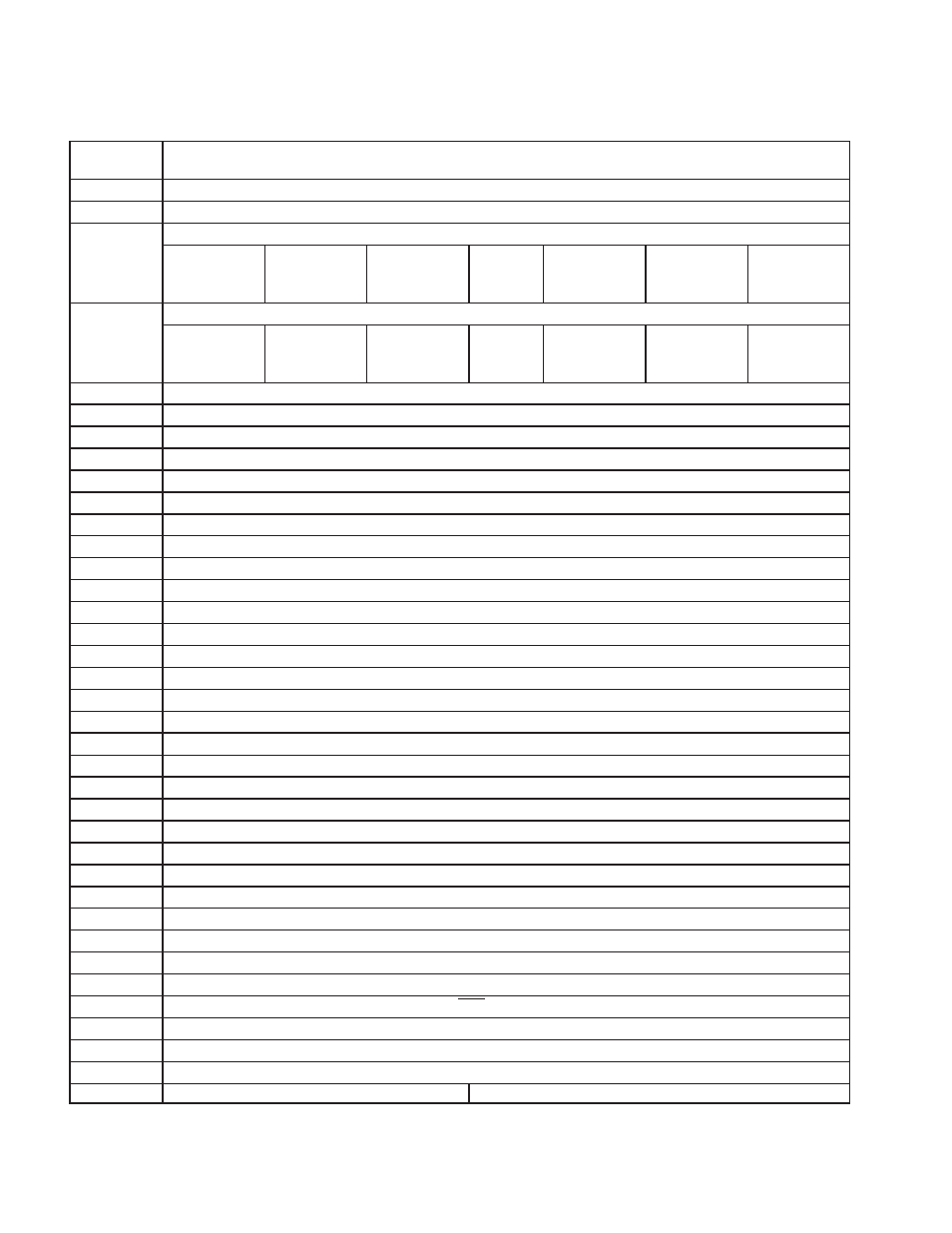

Table 3−9. EEPROM Loading Map

SERIAL ROM

OFFSET

BYTE DESCRIPTION

00h

CardBus function indicator (00h)

01h

Number of bytes (20h)

PCI 04h, command register, function 0, bits 8, 6−5, 2−0

02h

[7]

Command

register, bit 8

[6]

Command

register, bit 6

[5]

Command

register, bit 5

[4:3]

RSVD

[2]

Command

register, bit 2

[1]

Command

register, bit 1

[0]

Command

register, bit 0

PCI 04h, command register, function 1, bits 8, 6−5, 2−0

03h

[7]

Command

register, bit 8

[6]

Command

register, bit 6

[5]

Command

register, bit 5

[4:3]

RSVD

[2]

Command

register, bit 2

[1]

Command

register, bit 1

[0]

Command

register, bit 0

04h

PCI 40h, subsystem vendor ID, byte 0

05h

PCI 41h, subsystem vendor ID, byte 1

06h

PCI 42h, subsystem ID, byte 0

07h

PCI 43h, subsystem ID, byte 1

08h

PCI 44h, PC Card 16-bit I/F legacy mode base address register, byte 0, bits 7−1

09h

PCI 45h, PC Card 16-bit I/F legacy mode base address register, byte 1

0Ah

PCI 46h, PC Card 16-bit I/F legacy mode base address register, byte 2

0Bh

PCI 47h, PC Card 16-bit I/F legacy mode base address register, byte 3

0Ch

PCI 80h, system control, function 0, byte 0, bits 6−0

0Dh

PCI 80h, system control, function 1, byte 0, bit 2

0Eh

PCI 81h, system control, byte 1, bits 7,6

0Fh

Reserved nonloadable (PCI 82h, system control, byte 2)

10h

PCI 83h, system control, byte 3, bits 7−2, 0

11h

PCI 8Ch, MFUNC routing, byte 0

12h

PCI 8Dh, MFUNC routing, byte 1

13h

PCI 8Eh, MFUNC routing, byte 2

14h

PCI 8Fh, MFUNC routing, byte 3

15h

PCI 90h, retry status, bits 7, 6

16h

PCI 91h, card control, bit 7

17h

PCI 92h, device control, bits 6, 5, 3−0 (bit 0 must be programmed to 0)

18h

PCI 93h, diagnostic, bits 4−0

19h

PCI A2h, power-management capabilities, function 0, bit 15 (bit 7 of EEPROM offset 16h corresponds to bit 15)

1Ah

PCI A2h, power-management capabilities, function 1, bit 15 (bit 7 of EEPROM offset 16h corresponds to bit 15)

1Bh

CB Socket + 0Ch, function 0 socket force event, bit 27 (bit 3 of EEPROM offset 17h corresponds to bit 27)

1Ch

CB Socket + 0Ch, function 1 socket force event, bit 27 (bit 3 of EEPROM offset 18h corresponds to bit 27)

1Dh

ExCA 00h, ExCA identification and revision, bits 7−0

1Eh

PCI 86h, general control, byte 0, bits 7−0

1Fh

PCI 87h, general control, byte 1, bits 7, 6 (can only be set to 1 if bits 1:0 = 01), 4−0

20h

PCI 89h, GPE enable, bits 7, 6, 4−0

21h

PCI 8Bh, general-purpose output, bits 4−0

22h

1394 OHCI function indicator (02h)

23h

Number of bytes (17h)

24h

PCI 3Fh, maximum latency bits 7−4

PCI 3Eh, minimum grant, bits 3−0