Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 48

2−22

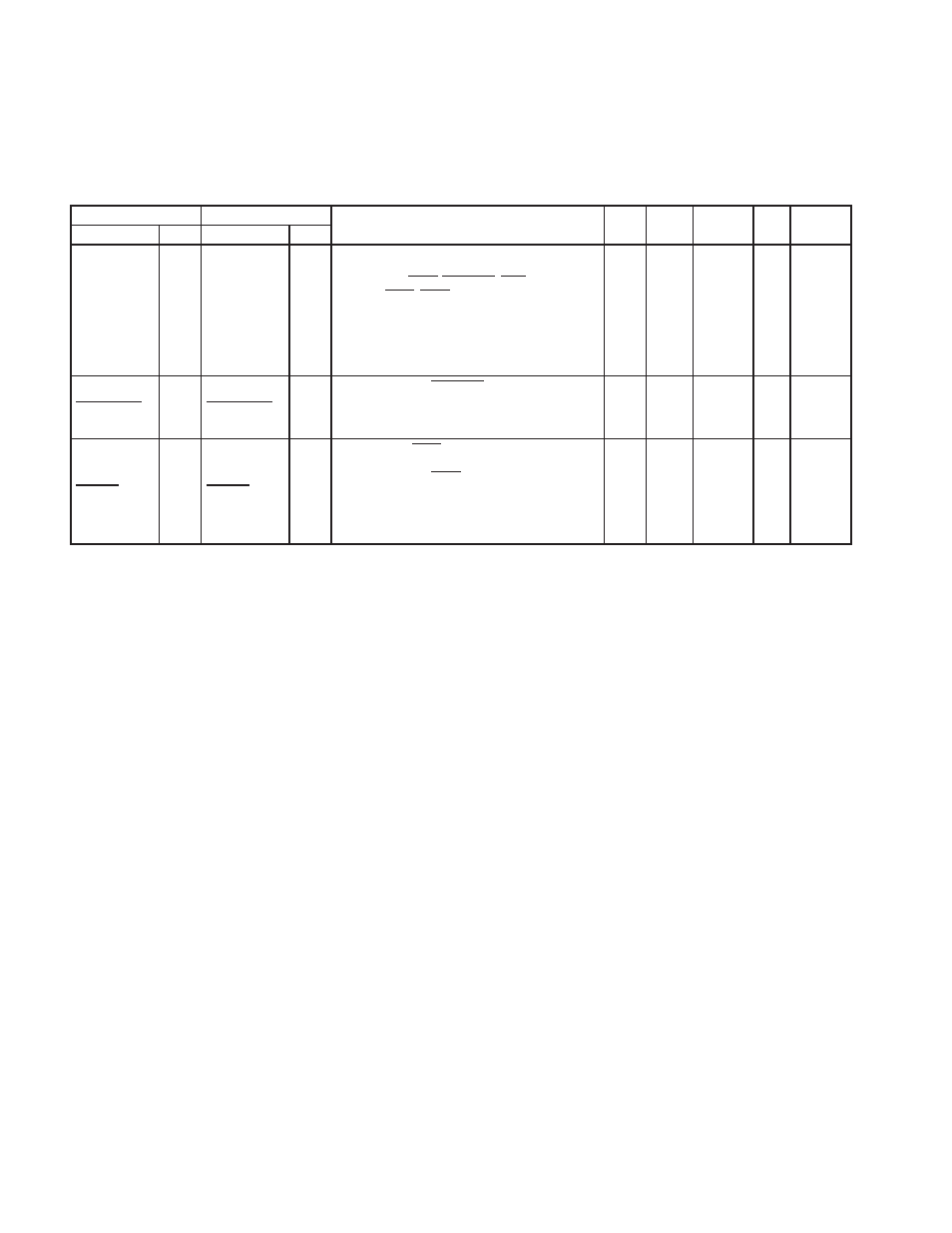

Table 2−12. CardBus PC Card Interface System Terminals

A 33-

Ω

to 47-

Ω

series damping resistor (per PC Card specification) is the only external component needed for

terminals B08 (A_CCLK) and H17 (B_CCLK). If any CardBus PC Card interface system terminal is unused, then the

terminal may be left floating.

SKT A TERMINAL

SKT B TERMINAL†

DESCRIPTION

I/O

INPUT

OUTPUT

PU/

POWER

NAME

NO.

NAME

NO.

DESCRIPTION

I/O

TYPE

INPUT

OUTPUT

PU/

PD

POWER

RAIL

A_CCLK

E09

B_CCLK

H18

CardBus clock. CCLK provides synchronous timing

for all transactions on the CardBus interface. All

signals except CRST, CCLKRUN, CINT, CSTSCHG,

CAUDIO, CCD2, CCD1, CVS2, and CVS1 are

sampled on the rising edge of CCLK, and all timing

parameters are defined with the rising edge of this

signal. CCLK operates at the PCI bus clock

frequency, but it can be stopped in the low state or

slowed down for power savings.

O

PCIO3

VCCA/

VCCB

A_CCLKRUN

C03

B_CCLKRUN

A18

CardBus clock run. CCLKRUN is used by a CardBus

PC Card to request an increase in the CCLK

frequency, and by the controller to indicate that the

CCLK frequency is going to be decreased.

I/O

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CRST

A06

B_CRST

F17

CardBus reset. CRST brings CardBus PC

Card-specific registers, sequencers, and signals to a

known state. When CRST is asserted, all CardBus

PC Card signals are placed in a high-impedance

state, and the controller drives these signals to a valid

logic level. Assertion can be asynchronous to CCLK,

but deassertion must be synchronous to CCLK.

O

PCII4

PCIO4

PU3

VCCA/

VCCB

† These terminals are reserved for the PCI7611 and PCI7411 controllers.