2 socket mask register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 155

6−3

6.2

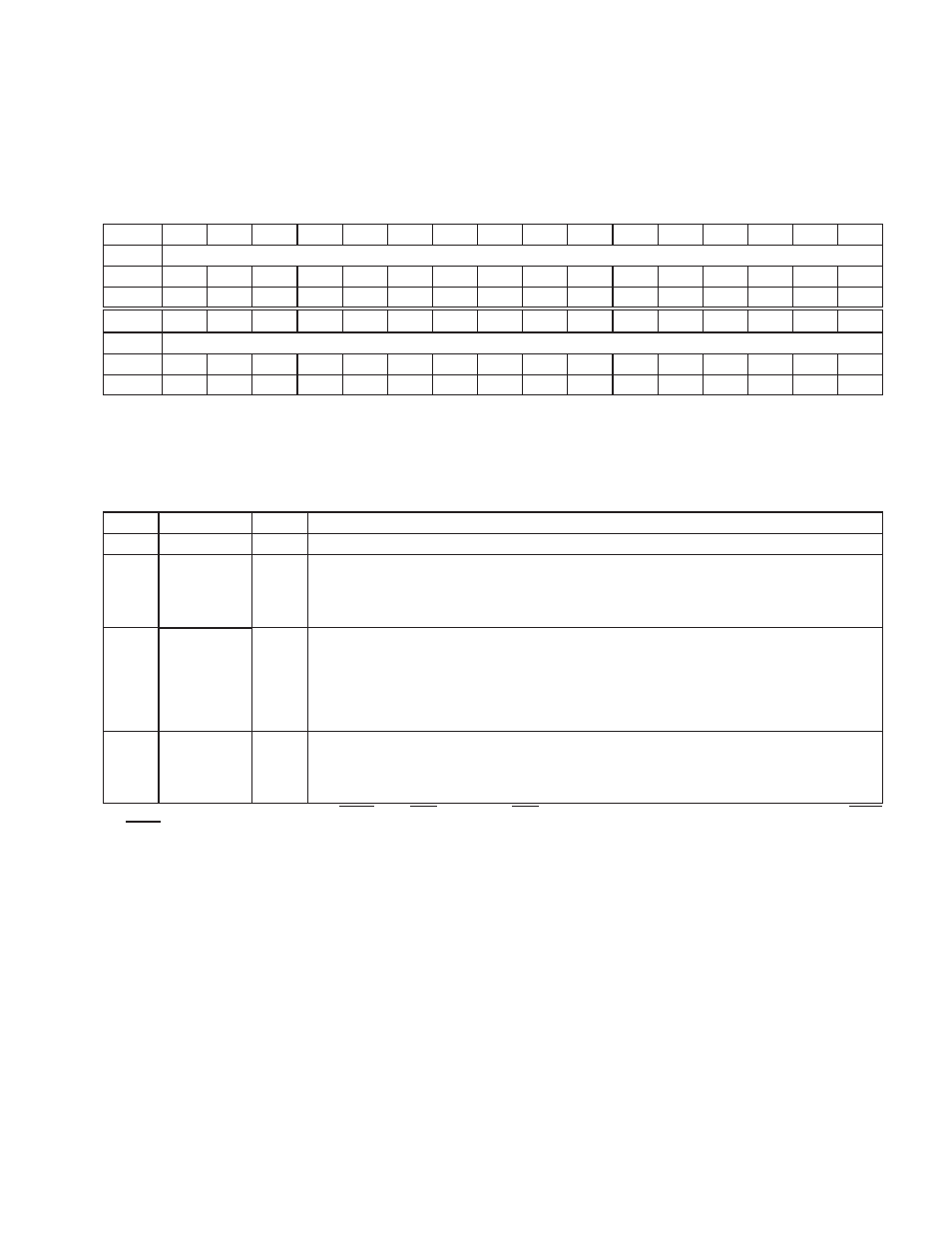

Socket Mask Register

This register allows software to control the CardBus card events which generate a status change interrupt. The state

of these mask bits does not prevent the corresponding bits from reacting in the socket event register (offset 00h, see

Section 6.1). See Table 6−3 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Socket mask

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Socket mask

Type

R

R

R

R

R

R

R

R

R

R

R

R

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Socket mask

Offset:

CardBus Socket Address + 04h

Type:

Read-only, Read/Write

Default: 0000 0000h

Table 6−3. Socket Mask Register Description

BIT

SIGNAL

TYPE

FUNCTION

31−4

RSVD

R

These bits return 0s when read.

3†

PWRMASK

RW

Power cycle. This bit masks the PWRCYCLE bit in the socket present state register (offset 08h, see

Section 6.3) from causing a status change interrupt.

0 = PWRCYCLE event does not cause a CSC interrupt (default).

1 = PWRCYCLE event causes a CSC interrupt.

2−1†

CDMASK

RW

Card detect mask. These bits mask the CDETECT1 and CDETECT2 bits in the socket present state

register (offset 08h, see Section 6.3) from causing a CSC interrupt.

00 = Insertion/removal does not cause a CSC interrupt (default).

01 = Reserved (undefined)

10 = Reserved (undefined)

11 = Insertion/removal causes a CSC interrupt.

0†

CSTSMASK

RW

CSTSCHG mask. This bit masks the CARDSTS field in the socket present state register (offset 08h, see

Section 6.3) from causing a CSC interrupt.

0 = CARDSTS event does not cause a CSC interrupt (default).

1 = CARDSTS event causes a CSC interrupt.

† This bit is cleared only by the assertion of GRST when PME is enabled. If PME is not enabled, then this bit is cleared by the assertion of PRST

or GRST.