40 asynchronous context control register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 218

8−38

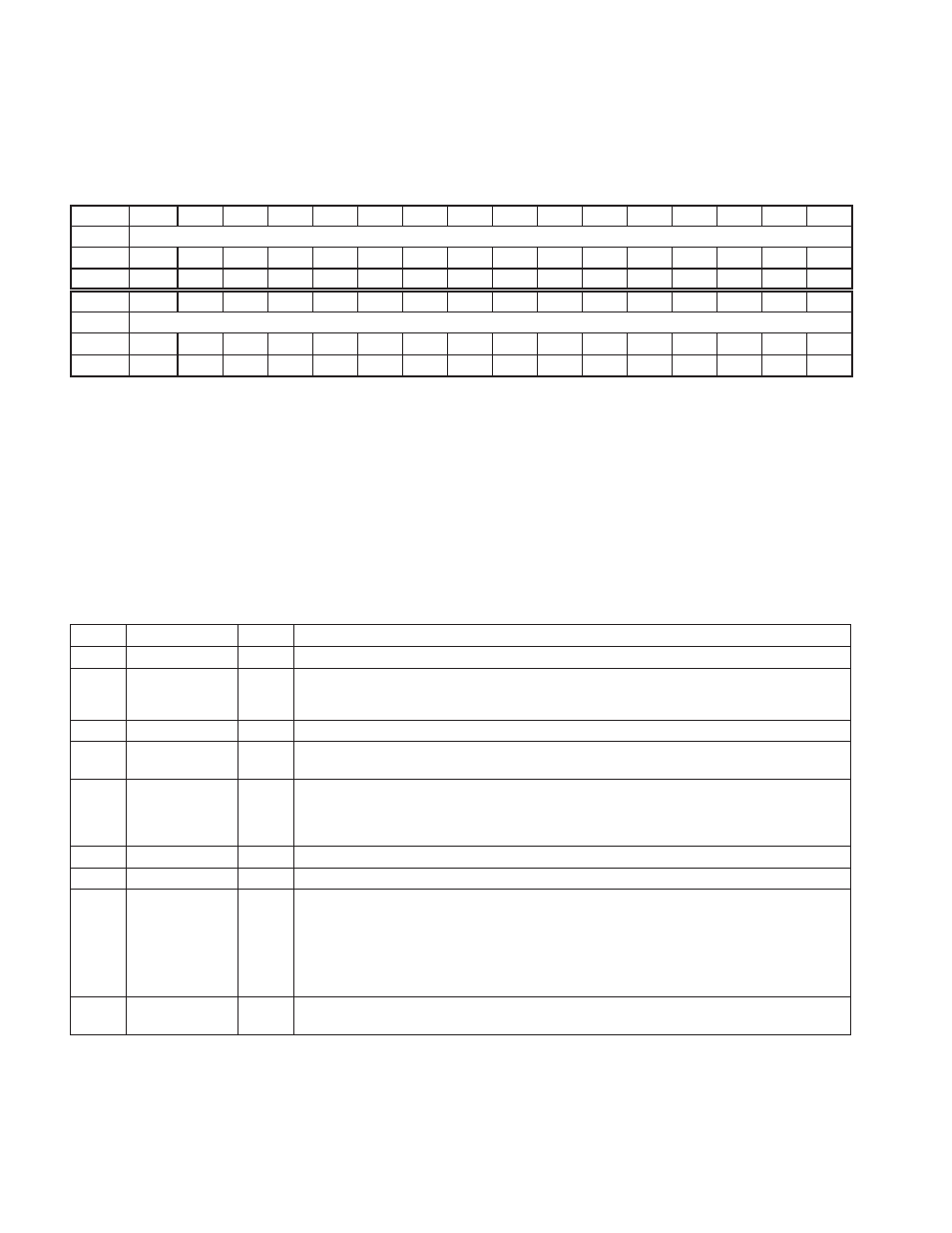

8.40 Asynchronous Context Control Register

The asynchronous context control set/clear register controls the state and indicates status of the DMA context. See

Table 8−31 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Asynchronous context control

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Asynchronous context control

Type

RSCU

R

R

RSU

RU

RU

R

R

RU

RU

RU

RU

RU

RU

RU

RU

Default

0

0

0

X

0

0

0

0

X

X

X

X

X

X

X

X

Register:

Asynchronous context control

Offset:

180h

set register

[ATRQ]

184h

clear register

[ATRQ]

1A0h

set register

[ATRS]

1A4h

clear register

[ATRS]

1C0h

set register

[ARRQ]

1C4h

clear register

[ARRQ]

1E0h

set register

[ARRS]

1E4h

clear register

[ARRS]

Type:

Read/Set/Clear/Update, Read/Set/Update, Read/Update, Read-only

Default:

0000 X0XXh

Table 8−31. Asynchronous Context Control Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31−16

RSVD

R

Reserved. Bits 31−16 return 0s when read.

15

run

RSCU

Bit 15 is set to 1 by software to enable descriptor processing for the context and cleared by software

to stop descriptor processing. The PCI7x21/PCI7x11 controller changes this bit only on a system

(hardware) or software reset.

14−13

RSVD

R

Reserved. Bits 14 and 13 return 0s when read.

12

wake

RSU

Software sets bit 12 to 1 to cause the PCI7x21/PCI7x11 controller to continue or resume descriptor

processing. The PCI7x21/PCI7x11 controller clears this bit on every descriptor fetch.

11

dead

RU

The PCI7x21/PCI7x11 controller sets bit 11 to 1 when it encounters a fatal error, and clears the bit when

software clears bit 15 (run). Asynchronous contexts supporting out-of-order pipelining provide unique

ContextControl.dead functionality. See Section 7.7 in the 1394 Open Host Controller Interface

Specification (Release 1.1) for more information.

10

active

RU

The PCI7x21/PCI7x11 controller sets bit 10 to 1 when it is processing descriptors.

9−8

RSVD

R

Reserved. Bits 9 and 8 return 0s when read.

7−5

spd

RU

This field indicates the speed at which a packet was received or transmitted and only contains

meaningful information for receive contexts. This field is encoded as:

000 = 100M bits/sec

001 = 200M bits/sec

010 = 400M bits/sec

All other values are reserved.

4−0

eventcode

RU

This field holds the acknowledge sent by the link core for this packet or an internally generated error

code if the packet was not transferred successfully.