Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 233

10−3

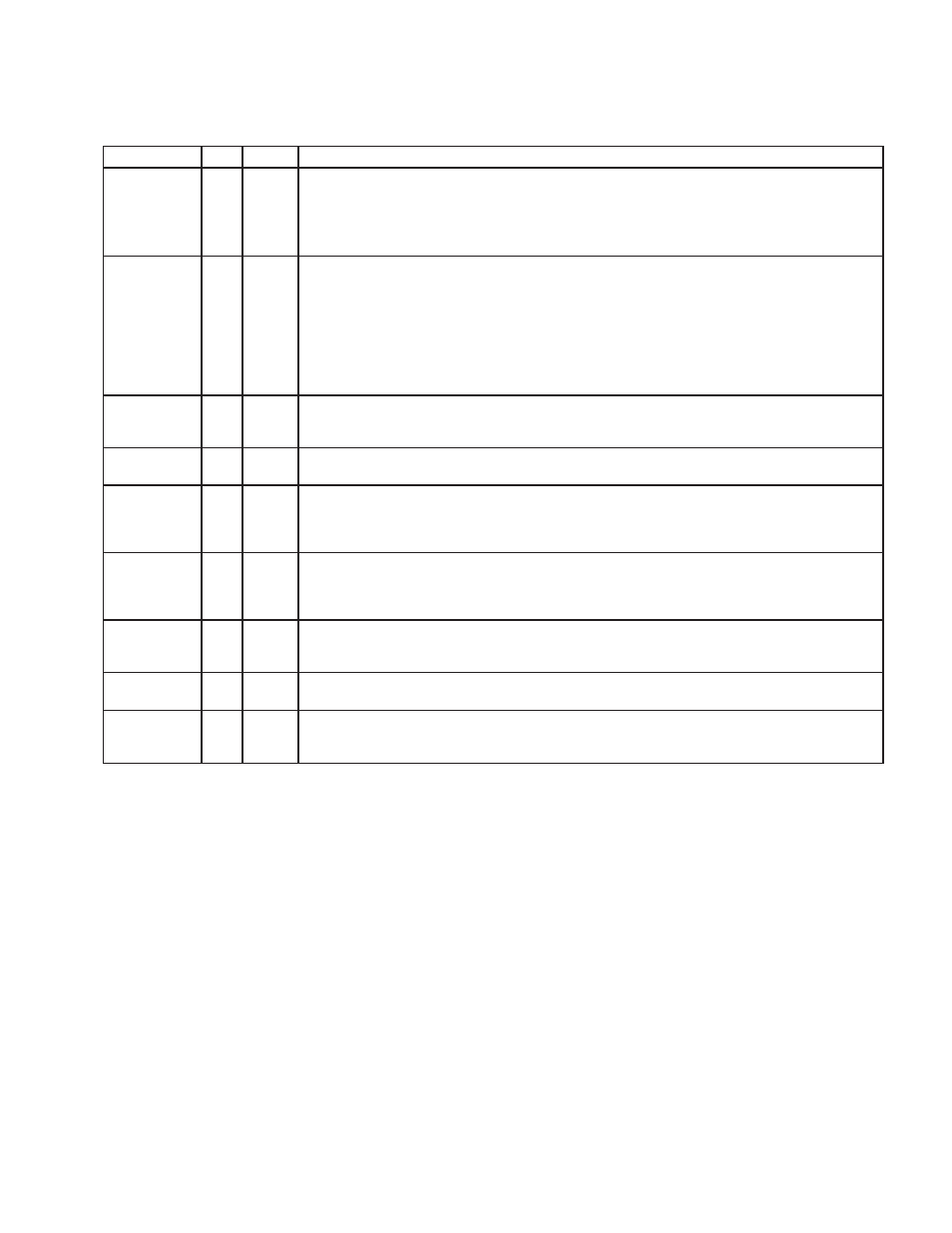

Table 10−2. Base Register Field Descriptions (Continued)

FIELD

SIZE

TYPE

DESCRIPTION

ISBR

1

R/W

Initiate short arbitrated bus reset. This bit, if set to 1, instructs the PHY layer to initiate a short (1.3

µ

s)

arbitrated bus reset at the next opportunity. This bit is cleared to 0 by a bus reset.

NOTE: Legacy IEEE Std 1394-1995 compliant PHY layers can not be capable of performing short bus

resets. Therefore, initiation of a short bus reset in a network that contains such a legacy device results in a

long bus reset being performed.

Loop

1

R/W

Loop detect. This bit is set to 1 when the arbitration controller times out during tree-ID start and may indicate

that the bus is configured in a loop. This bit is cleared to 0 by system (hardware) reset or by writing a 1 to this

register bit.

If the Loop and Watchdog bits are both set and the LLC is or becomes inactive, the PHY layer activates the

LLC to service the interrupt.

NOTE: If the network is configured in a loop, only those nodes which are part of the loop generate a

configuration-timeout interrupt. All other nodes instead time out waiting for the tree-ID and/or self-ID process

to complete and then generate a state time-out interrupt and bus-reset.

Pwr_fail

1

R/W

Cable power failure detect. This bit is set to 1 whenever the CPS input transitions from high to low indicating

that cable power may be too low for reliable operation. This bit is cleared to 0 by system (hardware) reset or

by writing a 1 to this register bit.

Timeout

1

R/W

State time-out interrupt. This bit indicates that a state time-out has occurred (which also causes a bus reset

to occur). This bit is cleared to 0 by system (hardware) reset or by writing a 1 to this register bit.

Port_event

1

R/W

Port event detect. This bit is set to 1 upon a change in the bias (unless disabled) connected, disabled, or fault

bits for any port for which the port interrupt enable (Int_enable) bit is set. Additionally, if the Watchdog bit is

set, the Port_event bit is set to 1 at the start of resume operations on any port. This bit is cleared to 0 by

system (hardware) reset or by writing a 1 to this register bit.

Enab_accel

1

R/W

Enable accelerated arbitration. This bit enables the PHY layer to perform the various arbitration acceleration

enhancements defined in IEEE Std 1394a-2000 (ACK-accelerated arbitration, asynchronous fly-by

concatenation, and isochronous fly-by concatenation). This bit is cleared to 0 by system (hardware) reset

and is unaffected by bus reset.

Enab_multi

1

R/W

Enable multispeed concatenated packets. This bit enables the PHY layer to transmit concatenated packets

of differing speeds in accordance with the protocols defined in IEEE Std 1394a-2000. This bit is cleared to 0

by system (hardware) reset and is unaffected by bus reset.

Page_Select

3

R/W

Page_Select. This field selects the register page to use when accessing register addresses 8 through 15.

This field is cleared to 0 by a system (hardware) reset and is unaffected by bus reset.

Port_Select

4

R/W

Port_Select. This field selects the port when accessing per-port status or control (for example, when one of

the port status/control registers is accessed in page 0). Ports are numbered starting at 0. This field is cleared

to 0 by system (hardware) reset and is unaffected by bus reset.