4 vendor-dependent register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 236

10−6

10.4 Vendor-Dependent Register

The vendor-dependent page provides access to the special control features of the PCI7x21/PCI7x11 controller, as

well as to configuration and status information used in manufacturing test and debug. This page is selected by writing

7 to the Page_Select field in base register 7. Table 10−7 shows the configuration of the vendor-dependent page, and

Table 10−8 shows the corresponding field descriptions.

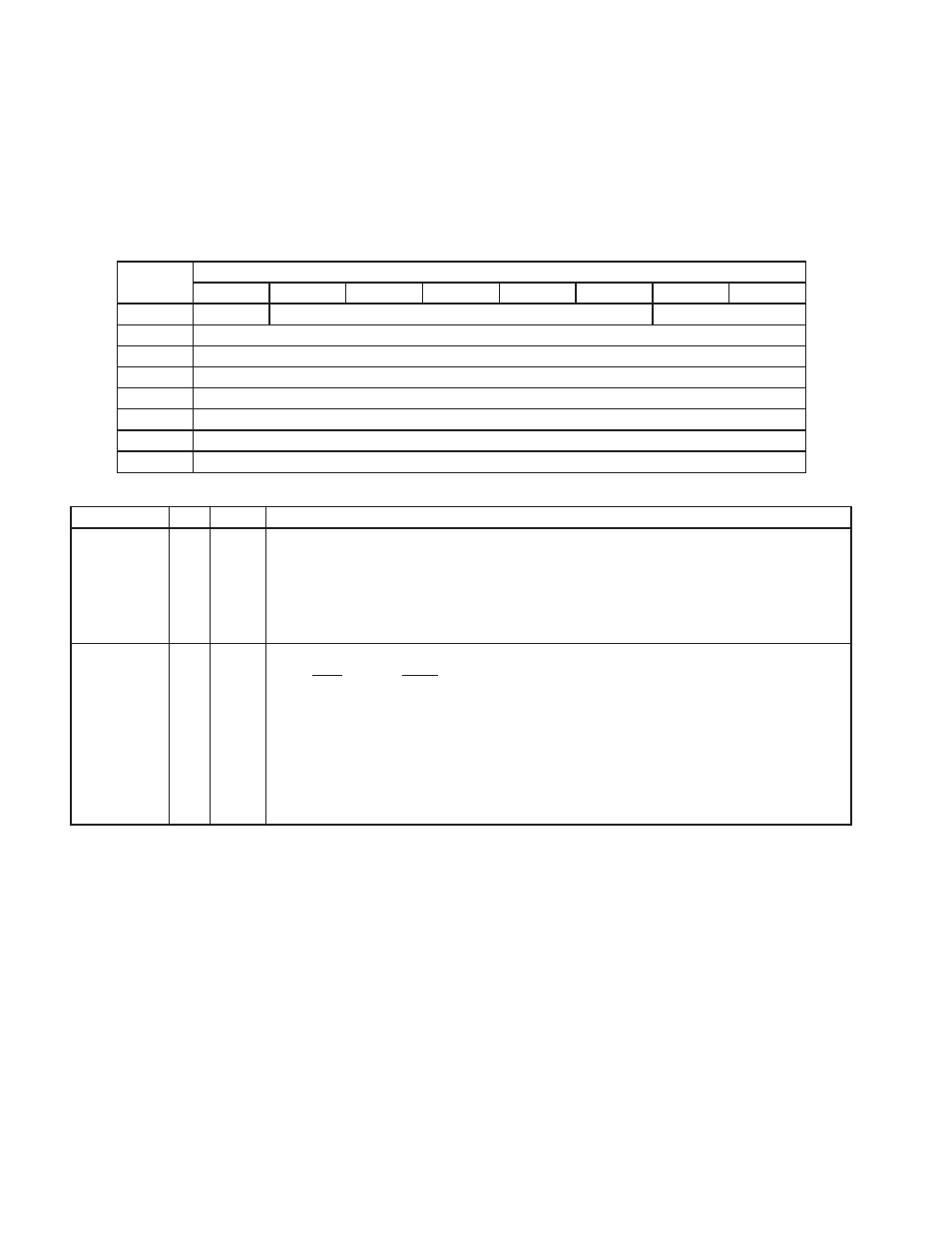

Table 10−7. Page 7 (Vendor-Dependent) Register Configuration

BIT POSITION

ADDRESS

0

1

2

3

4

5

6

7

1000

NPA

Reserved

Link_Speed

1001

Reserved for test

1010

Reserved for test

1011

Reserved for test

1100

Reserved for test

1101

Reserved for test

1110

Reserved for test

1111

Reserved for test

Table 10−8. Page 7 (Vendor-Dependent) Register Field Descriptions

FIELD

SIZE

TYPE

DESCRIPTION

NPA

1

RW

Null-packet actions flag. This bit instructs the PHY layer to not clear fair and priority requests when a null

packet is received with arbitration acceleration enabled. If this bit is set to 1, fair and priority requests are

cleared only when a packet of more than 8 bits is received; ACK packets (exactly 8 data bits), null packets

(no data bits), and malformed packets (less than 8 data bits) do not clear fair and priority requests. If this bit is

cleared to 0, fair and priority requests are cleared when any non-ACK packet is received, including null

packets or malformed packets of less than 8 bits. This bit is cleared to 0 by system (hardware) reset and is

unaffected by bus reset.

Link_Speed

2

RW

Link speed. This field indicates the top speed capability of the attached LLC. Encoding is as follows:

Code

Speed

00

S100

01

S200

10

S400

11

illegal

This field is replicated in the sp field of the self-ID packet to indicate the speed capability of the node (PHY

and LLC in combination). However, this field does not affect the PHY speed capability indicated to peer

PHYs during self-ID; the PCI7x21/PCI7x11 PHY layer identifies itself as S400 capable to its peers

regardless of the value in this field. This field is set to 10b (S400) by system (hardware) reset and is

unaffected by bus reset.