3 flash media (function 3) power management, 4 sd host (function 4) power management, 5 smart card (function 5) power management – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 82: 10 cardbus bridge power management

3−26

For more information on PCI power management, see the PCI Bus Power Management Interface Specification for

PCI to CardBus Bridges.

3.8.9.2 OHCI 1394 (Function 2) Power Management

The PCI7x21/PCI7x11 controller complies with the PCI Bus Power Management Interface Specification. The

controller supports the D0 (unitialized), D0 (active), D1, D2, and D3 power states as defined by the power

management definition in the 1394 Open Host Controller Interface Specification, Appendix A4.

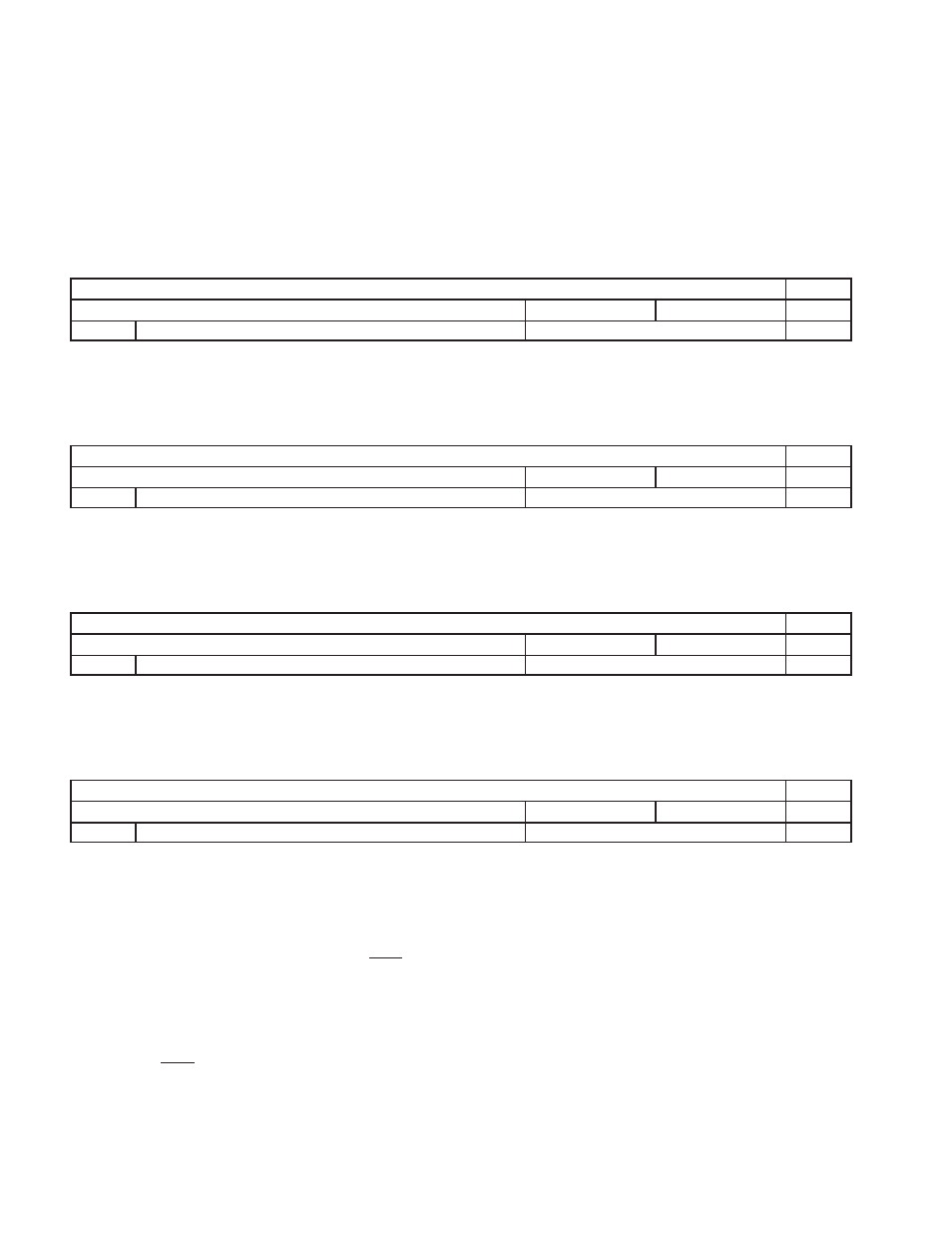

Table 3−16. Function 2 Power-Management Registers

REGISTER NAME

OFFSET

Power-management capabilities

Next item pointer

Capability ID

44h

Data

Power-management control/status register bridge support extensions

Power-management control/status (CSR)

48h

3.8.9.3 Flash Media (Function 3) Power Management

The PCI Bus Power Management Interface Specification is applicable for the flash media dedicated sockets. This

function supports the D0 and D3 power states.

Table 3−17. Function 3 Power-Management Registers

REGISTER NAME

OFFSET

Power-management capabilities

Next item pointer

Capability ID

44h

Data

Power-management control/status register bridge support extensions

Power-management control/status (CSR)

48h

3.8.9.4 SD Host (Function 4) Power Management

The PCI Bus Power Management Interface Specification is applicable for the SD host dedicated sockets. This

function supports the D0 and D3 power states.

Table 3−18. Function 4 Power-Management Registers

REGISTER NAME

OFFSET

Power-management capabilities

Next item pointer

Capability ID

80h

Data

Power-management control/status register bridge support extensions

Power-management control/status (CSR)

84h

3.8.9.5 Smart Card (Function 5) Power Management

The PCI Bus Power Management Interface Specification is applicable for the Smart Card dedicated sockets. This

function supports the D0 and D3 power states.

Table 3−19. Function 5 Power-Management Registers

REGISTER NAME

OFFSET

Power-management capabilities

Next item pointer

Capability ID

44h

Data

Power-management control/status register bridge support extensions

Power-management control/status (CSR)

48h

3.8.10 CardBus Bridge Power Management

The PCI Bus Power Management Interface Specification for PCI to CardBus Bridges was approved by PCMCIA in

December of 1997. This specification follows the device and bus state definitions provided in the PCI Bus Power

Management Interface Specification published by the PCI Special Interest Group (SIG). The main issue addressed

in the PCI Bus Power Management Interface Specification for PCI to CardBus Bridges is wake-up from D3

hot

or D3

cold

without losing wake-up context (also called PME context).

The specific issues addressed by the PCI Bus Power Management Interface Specification for PCI to CardBus Bridges

for D3 wake-up are as follows:

•

Preservation of device context. The specification states that a reset must occur during the transition from

D3 to D0. Some method to preserve wake-up context must be implemented so that the reset does not clear

the PME context registers.

•

Power source in D3

cold

if wake-up support is required from this state.