5 class code and revision id register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 259

12−5

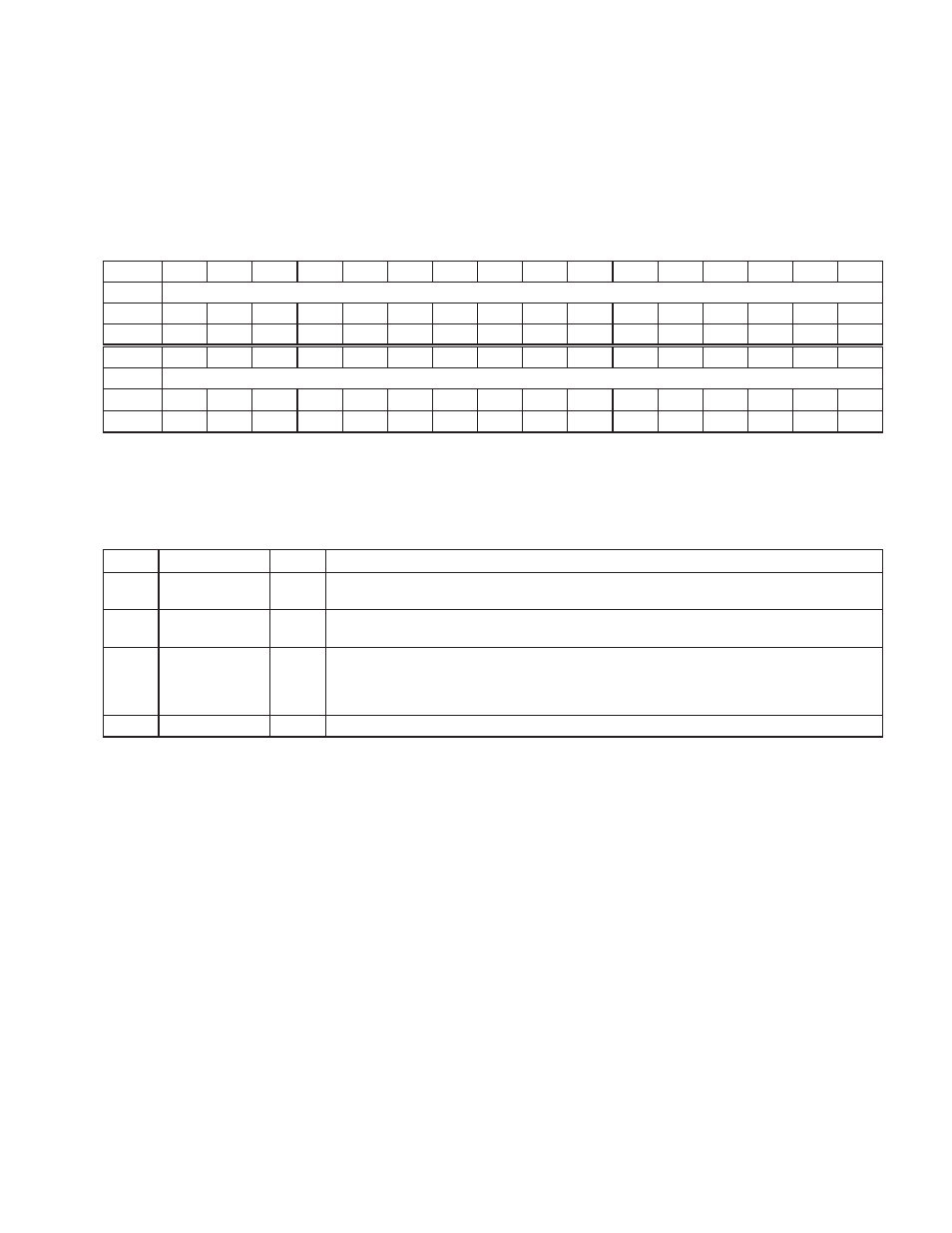

12.5 Class Code and Revision ID Register

The class code and revision ID register categorizes the base class, subclass, and programming interface of the

function. The base class is 08h, identifying the controller as a generic system peripheral. The subclass is 05h,

identifying the function as an SD host controller. The programming interface is 01h, indicating that the function is a

standard SD host with DMA capabilities. Furthermore, the TI chip revision is indicated in the least significant byte

(00h). See Table 12−4 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Class code and revision ID

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

1

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Class code and revision ID

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

X

X

X

X

X

X

X

X

X

Register:

Class code and revision ID

Offset:

08h

Type:

Read-only

Default:

0805 0XXXh

Table 12−4. Class Code and Revision ID Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31−24

BASECLASS

R

Base class. This field returns 08h when read, which broadly classifies the function as a generic system

peripheral.

23−16

SUBCLASS

R

Subclass. This field returns 05h when read, which specifically classifies the function as an SD host

controller.

15−8

PGMIF

R

Programming interface. If bit 0 (DMA_EN) in the general control register is 0, then this field returns 00h

when read to indicate that the function is a standard SD host without DMA capabilities. If the DMA_EN

bit is 1, then this field returns 01h when read to indicate that the function is a standard SD host with

DMA capabilities.

7−0

CHIPREV

R

Silicon revision. This field returns the silicon revision of the SD host controller.