22 cardbus i/o limit registers 0, 1, 23 interrupt line register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 103

4−13

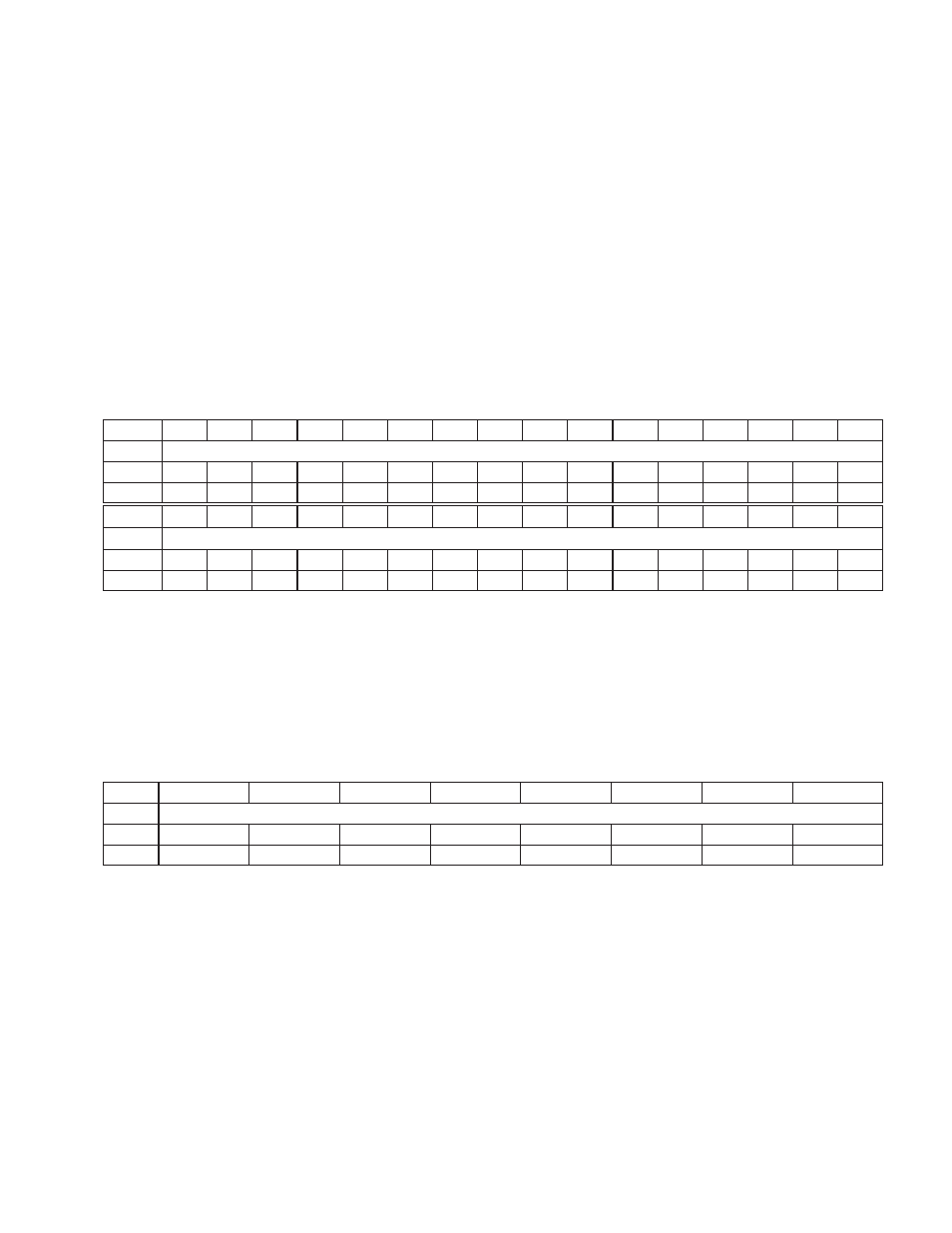

4.22 CardBus I/O Limit Registers 0, 1

These registers indicate the upper address of a PCI I/O address range. They are used by the PCI7x21/PCI7x11

controller to determine when to forward an I/O transaction to the CardBus bus, and likewise, when to forward a

CardBus cycle to PCI. The lower 16 bits of this register locate the top of the I/O window within a 64-Kbyte page, and

the upper 16 bits are a page register which locates this 64-Kbyte page in 32-bit PCI I/O address space. Bits 15−2

are read/write and allow the I/O limit address to be located anywhere in the 64-Kbyte page (indicated by bits 31−16

of the appropriate I/O base register) on doubleword boundaries.

Bits 31−16 are read-only and always return 0s when read. The page is set in the I/O base register. Bits 15−2 are

read/write and bits 1−0 are read-only, returning 00 or 01 when read, depending on the value of bit 12 (IO_LIMIT_SEL)

in the general control register (PCI offset 86h, see Section 4.31). Writes to read-only bits have no effect.

These I/O windows are enabled when either the I/O base register or the I/O limit register is nonzero. By default, the

I/O windows are not enabled to pass the first doubleword of I/O to CardBus.

Either the I/O base register or the I/O limit register must be nonzero to enable any I/O transactions.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

I/O limit registers 0, 1

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

I/O limit registers 0, 1

Type

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

X

Register:

I/O limit registers 0, 1

Offset:

30h, 38h

Type:

Read-only, Read/Write

Default: 0000 000Xh

4.23 Interrupt Line Register

The interrupt line register is a read/write register used by the host software. As part of the interrupt routing procedure,

the host software writes this register with the value of the system IRQ assigned to the function.

Bit

7

6

5

4

3

2

1

0

Name

Interrupt line

Type

RW

RW

RW

RW

RW

RW

RW

RW

Default

1

1

1

1

1

1

1

1

Register:

Interrupt line

Offset:

3Ch

Type:

Read/Write

Default: FFh