21 power management data register, 22 general control register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 285

13−13

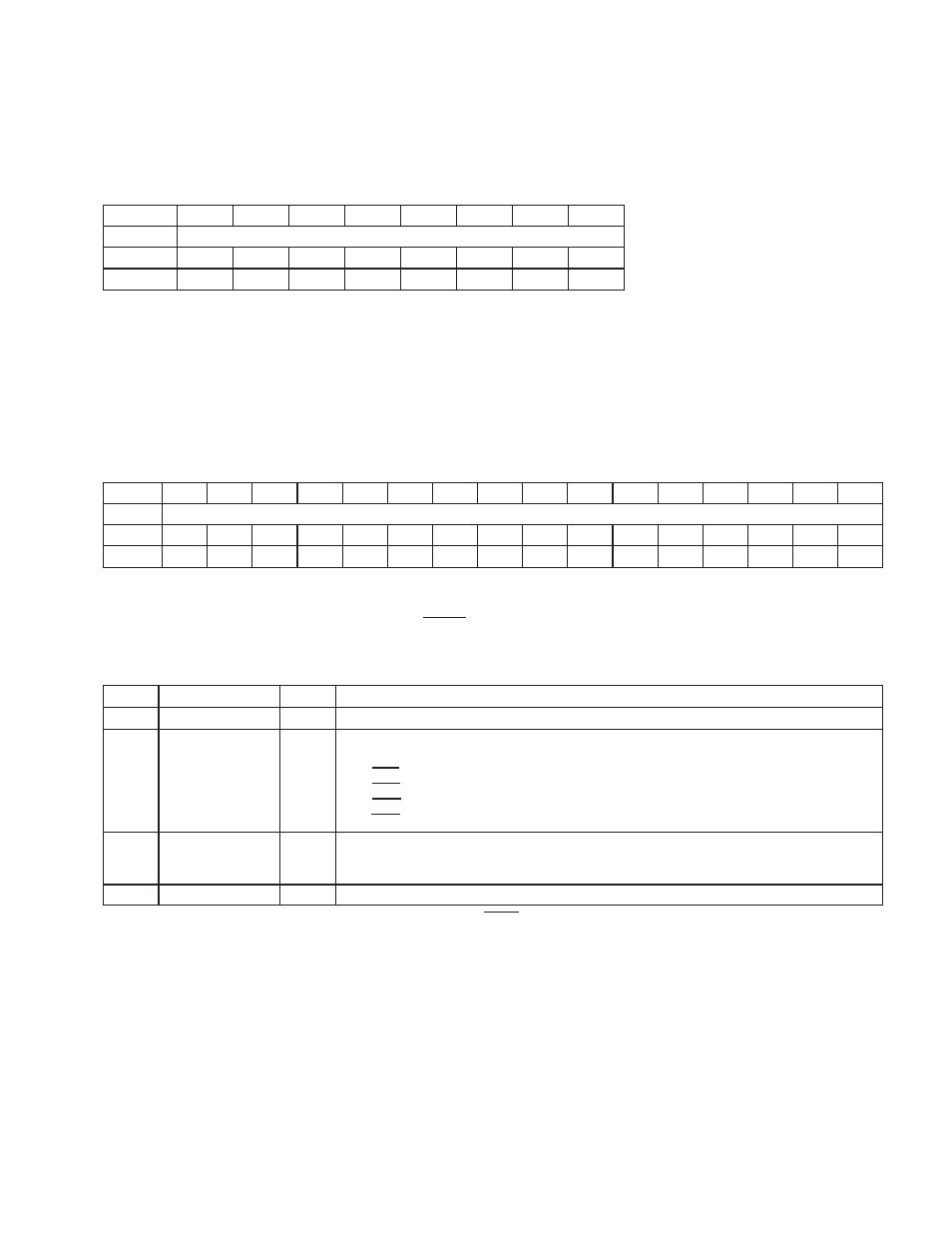

13.21 Power Management Data Register

The power management bridge support extension register provides extended power-management features not

applicable to the Smart Card controller; thus, it is read-only and returns 0 when read.

Bit

7

6

5

4

3

2

1

0

Name

Power management data

Type

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

Register:

Power management data

Offset:

4Bh

Type:

Read-only

Default:

00h

13.22 General Control Register

This register controls this function. Information of this register can be read from the socket configuration register in

the Smart Card socket control register set. See Table 13−13 for a complete description of the register contents.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

General control

Type

R

R

R

R

R

R

R

R

R

RW

RW

RW

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

General control

Offset:

4Ch

Type:

Read/Write (EEPROM, GRST only)

Default:

0000h

Table 13−13. General Control Register

BIT

FIELD NAME

TYPE

DESCRIPTION

15−7

RSVD

R

Reserved. Bits 15−7 return 0s when read.

6−5 ‡

INT_SEL

RW

Interrupt select. These bits are program the INTPIN register and set which interrupt output is used.

This field is ignored if one of the USE_INTx terminals is asserted.

00 = INTA (pin = 1)

01 = INTB (pin = 2)

10 = INTC (pin = 3)

11 = INTD (pin = 4)

4 ‡

D3_COLD

RW

Disable function. Setting this bit to 1 hides this function. PCI configuration register of this function

must be accessible at any time. Clock (PCI and 48 MHz) to the rest of the function blocks must be

gated to reduce power consumption.

3−0

RSVD

R

Reserved. Bits 3−0 return 0s when read.

‡ One or more bits in this register are cleared only by the assertion of GRST.