26 isochronous receive interrupt mask register, 27 initial bandwidth available register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 205

8−25

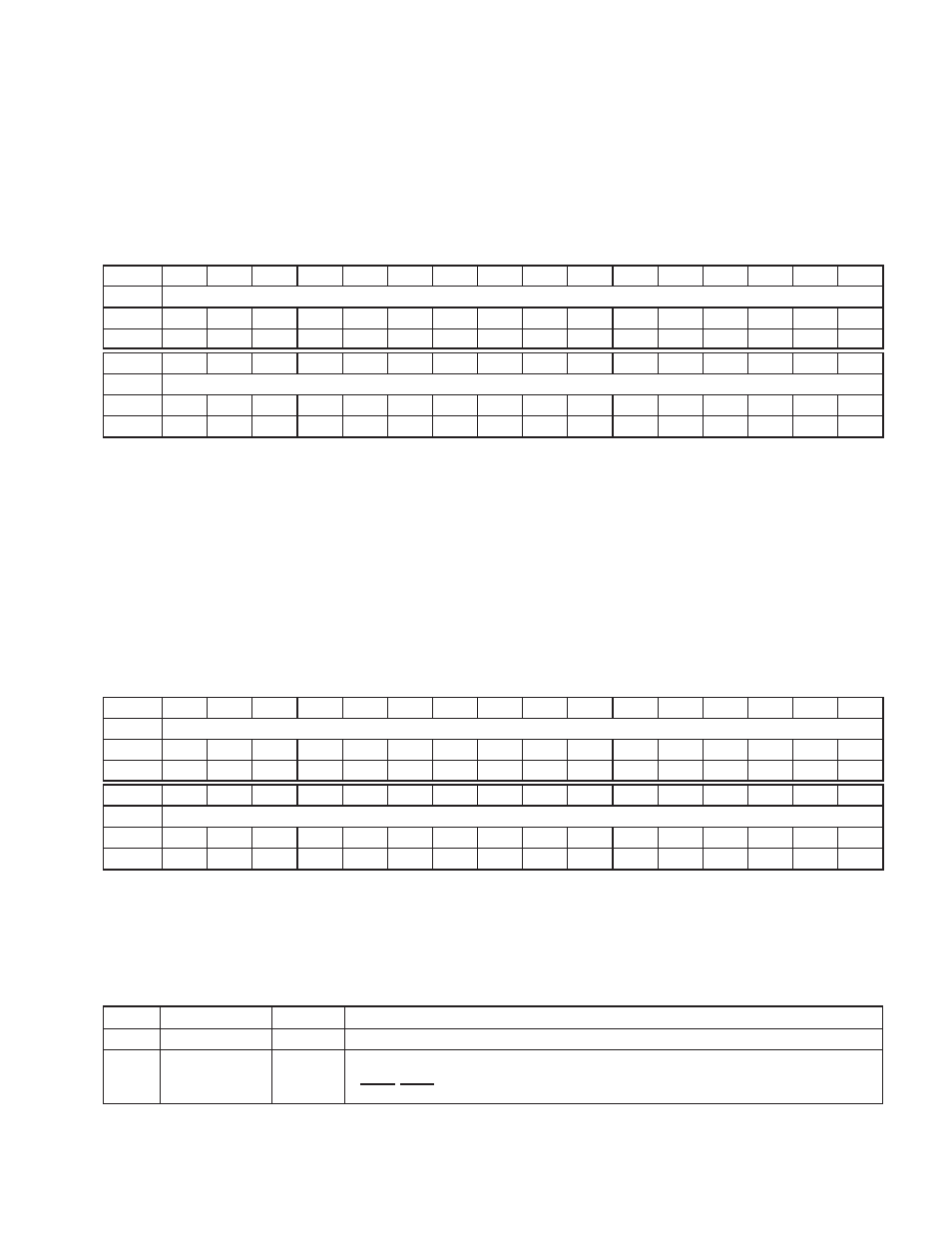

8.26 Isochronous Receive Interrupt Mask Register

The isochronous receive interrupt mask set/clear register enables the isochRx interrupt source on a per-channel

basis. Reads from either the set register or the clear register always return the contents of the isochronous receive

interrupt mask register. In all cases the enables for each interrupt event align with the isochronous receive interrupt

event register bits detailed in Table 8−18.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Isochronous receive interrupt mask

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Isochronous receive interrupt mask

Type

R

R

R

R

R

R

R

R

R

R

R

R

RSC

RSC

RSC

RSC

Default

0

0

0

0

0

0

0

0

0

0

0

0

X

X

X

X

Register:

Isochronous receive interrupt mask

Offset:

A8h

set register

ACh

clear register

Type:

Read/Set/Clear, Read-only

Default:

0000 000Xh

8.27 Initial Bandwidth Available Register

The initial bandwidth available register value is loaded into the corresponding bus management CSR register on a

system (hardware) or software reset. See Table 8−19 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Initial bandwidth available

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Initial bandwidth available

Type

R

R

R

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Default

0

0

0

1

0

0

1

1

0

0

1

1

0

0

1

1

Register:

Initial bandwidth available

Offset:

B0h

Type:

Read-only, Read/Write

Default:

0000 1333h

Table 8−19. Initial Bandwidth Available Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31−13

RSVD

R

Reserved. Bits 31−13 return 0s when read.

12−0

InitBWAvailable

RW

This field is reset to 1333h on a system (hardware) or software reset, and is not affected by a 1394

bus reset. The value of this field is loaded into the BANDWIDTH_AVAILABLE CSR register upon

a GRST, PRST, or a 1394 bus reset.