7 header type and bist register, 8 flash media base address register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 244

11−6

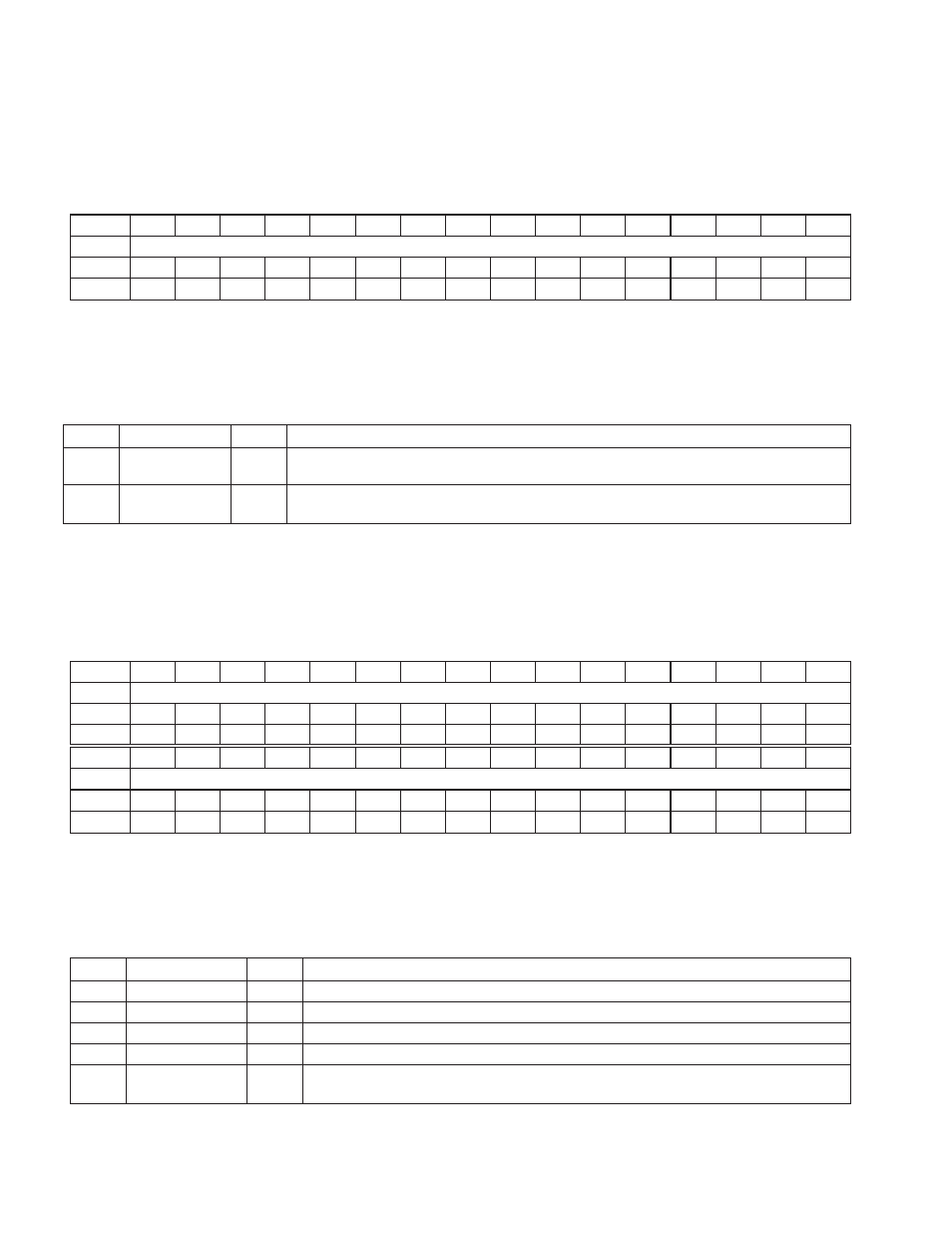

11.7 Header Type and BIST Register

The header type and built-in self-test (BIST) register indicates the flash media controller PCI header type and no

built-in self-test. See Table 11−6 for a complete description of the register contents.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Header type and BIST

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

Register:

Header type and BIST

Offset:

0Eh

Type:

Read-only

Default:

0080h

Table 11−6. Header Type and BIST Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

15−8

BIST

R

Built-in self-test. The flash media controller does not include a BIST; therefore, this field returns 00h

when read.

7−0

HEADER_TYPE

R

PCI header type. The flash media controller includes the standard PCI header. Bit 7 indicates if the flash

media is a multifunction device.

11.8 Flash Media Base Address Register

The flash media base address register specifies the base address of the memory-mapped interface registers. Since

the implementation of the flash media controller core in the PCI7x21/PCI7x11 controller contains 2 sockets, the size

of the base address register is 4096 bytes. See Table 11−7 for a complete description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Flash media base address

Type

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Flash media base address

Type

RW

RW

RW

RW

RW

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Register:

Flash media base address

Offset:

10h

Type:

Read/Write, Read-only

Default:

0000 0000h

Table 11−7. Flash Media Base Address Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31−13

BAR

RW

Base address. This field specifies the upper bits of the 32-bit starting base address.

12−4

RSVD

R

Reserved. Bits 12−4 return 0s when read to indicate that the size of the base address is 8192 bytes.

3

PREFETCHABLE

R

Prefetchable. Since this base address is not prefetchable, bit 3 returns 0 when read.

2−1

RSVD

R

Reserved. Bits 2−1 return 0s when read.

0

MEM_INDICATOR

R

Memory space indicator. Bit 0 is hardwired to 0 to indicate that the base address maps into memory

space.