11 flash media controller programming model – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 239

11−1

11 Flash Media Controller Programming Model

This section describes the internal PCI configuration registers used to program the PCI7x21/PCI7x11 flash media

controller interface. All registers are detailed in the same format: a brief description for each register is followed by

the register offset and a bit table describing the reset state for each register.

A bit description table, typically included when the register contains bits of more than one type or purpose, indicates

bit field names, a detailed field description, and field access tags which appear in the type column. Table 4−1

describes the field access tags.

The PCI7x21/PCI7x11 controller is a multifunction PCI device. The flash media controller core is integrated as PCI

function 3. The function 3 configuration header is compliant with the PCI Local Bus Specification as a standard

header. Table 11−1 illustrates the configuration header that includes both the predefined portion of the configuration

space and the user-definable registers.

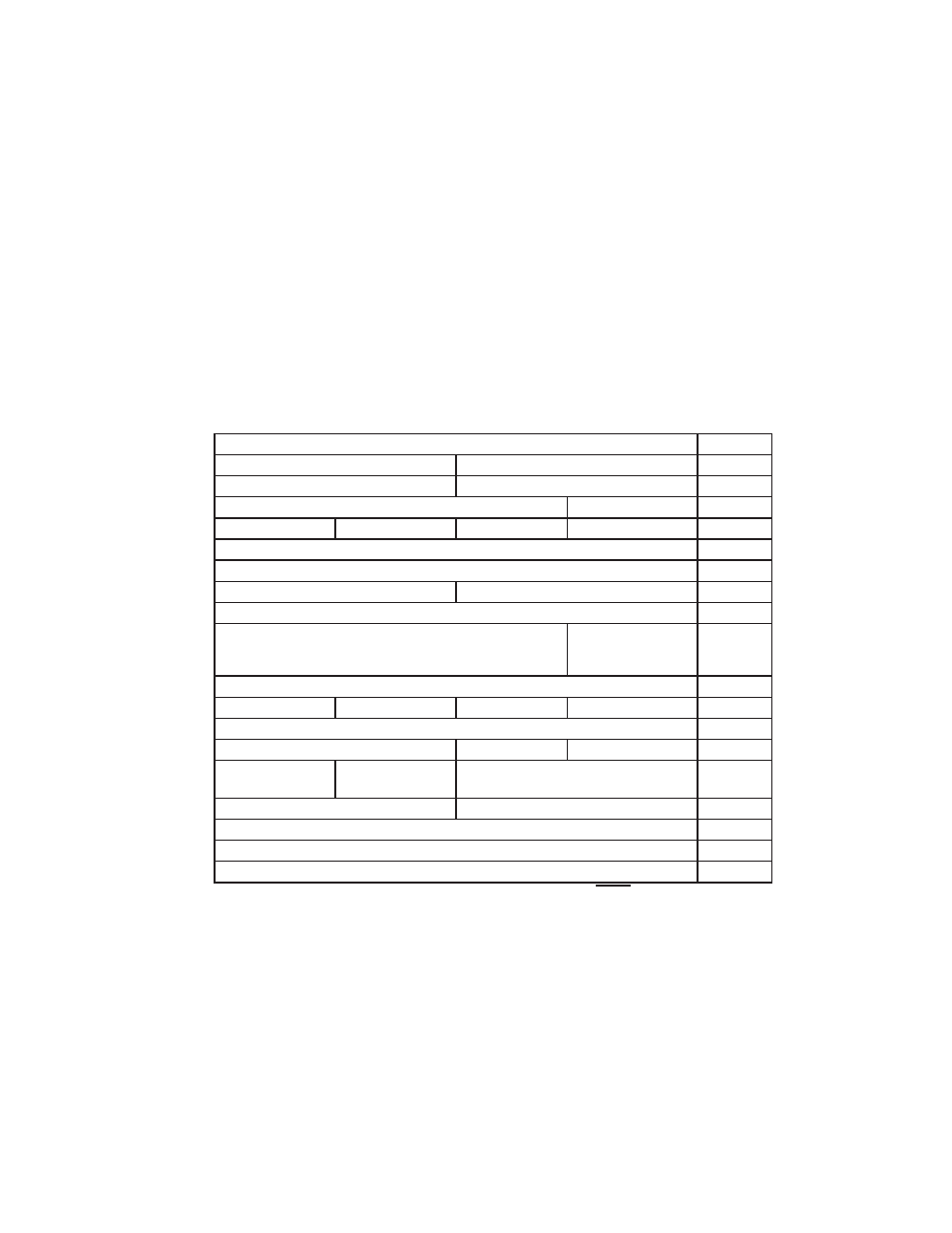

Table 11−1. Function 3 Configuration Register Map

REGISTER NAME

OFFSET

Device ID

Vendor ID

00h

Status

Command

04h

Class code

Revision ID

08h

BIST

Header type

Latency timer

Cache line size

0Ch

Flash media base address

10h

Reserved

14h−28h

Subsystem ID ‡

Subsystem vendor ID ‡

2Ch

Reserved

30h

Reserved

PCI power

management

capabilities pointer

34h

Reserved

38h

Maximum latency

Minimum grant

Interrupt pin

Interrupt line

3Ch

Reserved

40h

Power management capabilities

Next item pointer

Capability ID

44h

PM data

(Reserved)

PMCSR_BSE

Power management control and status ‡

48h

Reserved

General control ‡

4Ch

Subsystem access

50h

Diagnostic ‡

54h

Reserved

58h−FCh

‡ One or more bits in this register are cleared only by the assertion of GRST.