Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 146

5−18

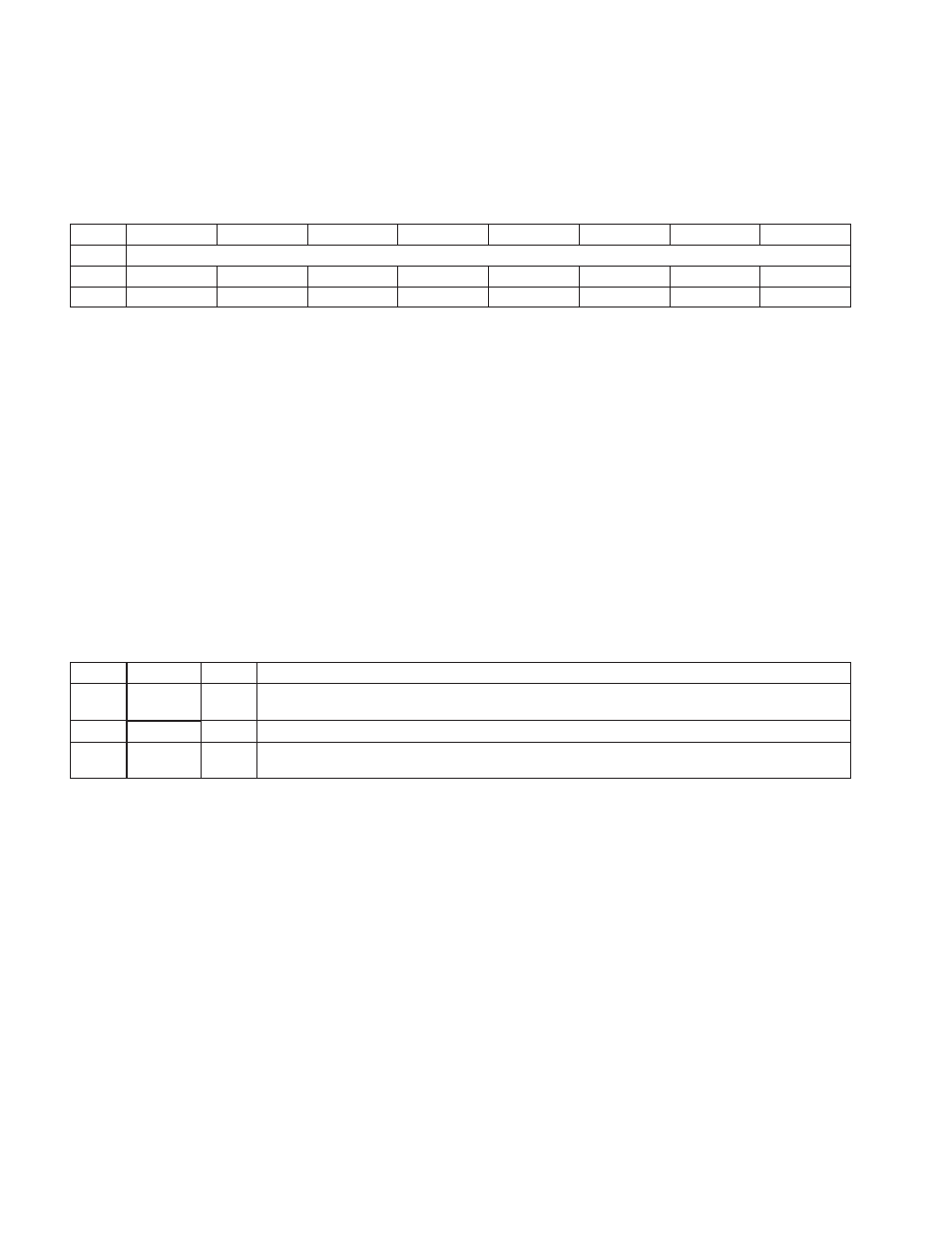

5.16 ExCA Memory Windows 0−4 End-Address High-Byte Registers

These registers contain the high nibble of the 16-bit memory window end address for memory windows 0, 1, 2, 3,

and 4. The lower 4 bits of these registers correspond to bits A23−A20 of the end address. In addition, the memory

window wait states are set in this register. See Table 5−12 for a complete description of the register contents.

Bit

7

6

5

4

3

2

1

0

Name

ExCA memory windows 0−4 end-address high-byte

Type

RW

RW

R

R

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

Register:

ExCA memory window 0 end-address high-byte

Offset:

CardBus Socket Address + 813h:

Card A ExCA Offset 13h

Card B ExCA Offset 53h

Register:

ExCA memory window 1 end-address high-byte

Offset:

CardBus Socket Address + 81Bh:

Card A ExCA Offset 1Bh

Card B ExCA Offset 5Bh

Register:

ExCA memory window 2 end-address high-byte

Offset:

CardBus Socket Address + 823h:

Card A ExCA Offset 23h

Card B ExCA Offset 63h

Register:

ExCA memory window 3 end-address high-byte

Offset:

CardBus Socket Address + 82Bh:

Card A ExCA Offset 2Bh

Card B ExCA Offset 6Bh

Register:

ExCA Memory window 4 end-address high-byte

Offset:

CardBus Socket Address + 833h:

Card A ExCA Offset 33h

Card B ExCA Offset 73h

Type:

Read/Write, Read-only

Default: 00h

Table 5−12. ExCA Memory Windows 0−4 End-Address High-Byte Registers Description

BIT

SIGNAL

TYPE

FUNCTION

7−6

MEMWS

RW

Wait state. These bits specify the number of equivalent ISA wait states to be added to 16-bit memory

accesses. The number of wait states added is equal to the binary value of these 2 bits.

5−4

RSVD

R

Reserved. These bits return 0s when read. Writes have no effect.

3−0

ENDHN

RW

End-address high nibble. These bits represent the upper address bits A23−A20 of the memory window end

address.