31 link control register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 208

8−28

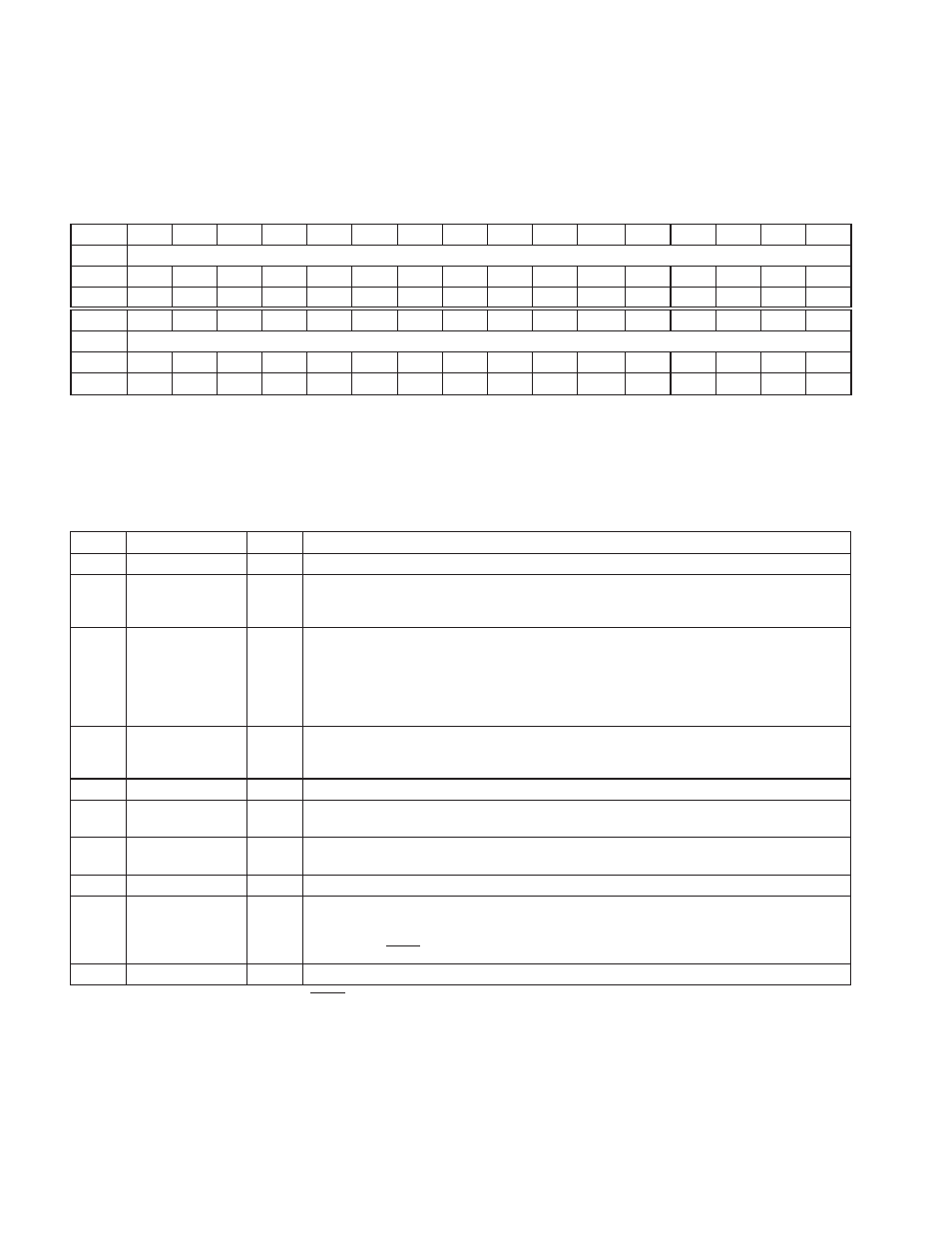

8.31 Link Control Register

The link control set/clear register provides the control flags that enable and configure the link core protocol portions

of the PCI7x21/PCI7x11 controller. It contains controls for the receiver and cycle timer. See Table 8−23 for a complete

description of the register contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Link control

Type

R

R

R

R

R

R

R

R

R

RSC

RSCU

RSC

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

X

X

X

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Link control

Type

R

R

R

R

R

RSC

RSC

R

R

RS

R

R

R

R

R

R

Default

0

0

0

0

0

X

X

0

0

0

0

0

0

0

0

0

Register:

Link control

Offset:

E0h

set register

E4h

clear register

Type:

Read/Set/Clear/Update, Read/Set/Clear, Read-only

Default:

00X0 0X00h

Table 8−23. Link Control Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

31−23

RSVD

R

Reserved. Bits 31−23 return 0s when read.

22

cycleSource

RSC

When bit 22 is set to 1, the cycle timer uses an external source (CYCLEIN) to determine when to roll

over the cycle timer. When this bit is cleared, the cycle timer rolls over when the timer reaches

3072 cycles of the 24.576-MHz clock (125

µ

s).

21

cycleMaster

RSCU

When bit 21 is set to 1, the PCI7x21/PCI7x11 controller is root and it generates a cycle start packet

every time the cycle timer rolls over, based on the setting of bit 22 (cycleSource). When bit 21 is

cleared, the OHCI-Lynx

accepts received cycle start packets to maintain synchronization with the

node which is sending them. Bit 21 is automatically cleared when bit 25 (cycleTooLong) in the

interrupt event register at OHCI offset 80h/84h (see Section 8.21) is set to 1. Bit 21 cannot be set to

1 until bit 25 (cycleTooLong) is cleared.

20

CycleTimerEnable

RSC

When bit 20 is set to 1, the cycle timer offset counts cycles of the 24.576-MHz clock and rolls over

at the appropriate time, based on the settings of the above bits. When this bit is cleared, the cycle

timer offset does not count.

19−11

RSVD

R

Reserved. Bits 19−11 return 0s when read.

10

RcvPhyPkt

RSC

When bit 10 is set to 1, the receiver accepts incoming PHY packets into the AR request context if

the AR request context is enabled. This bit does not control receipt of self-identification packets.

9

RcvSelfID

RSC

When bit 9 is set to 1, the receiver accepts incoming self-identification packets. Before setting this

bit to 1, software must ensure that the self-ID buffer pointer register contains a valid address.

8−7

RSVD

R

Reserved. Bits 8 and 7 return 0s when read.

6 ‡

tag1SyncFilterLock

RS

When bit 6 is set to 1, bit 6 (tag1SyncFilter) in the isochronous receive context match register (see

Section 8.46) is set to 1 for all isochronous receive contexts. When bit 6 is cleared, bit 6

(tag1SyncFilter) in the isochronous receive context match register has read/write access. This bit is

cleared when GRST is asserted.

5−0

RSVD

R

Reserved. Bits 5−0 return 0s when read.

‡ This bit is cleared only by the assertion of GRST.