46 power-management data register – Texas Instruments Dual/Single Socket CardBus and UntraMedia Controller PCI7621 User Manual

Page 124

4−34

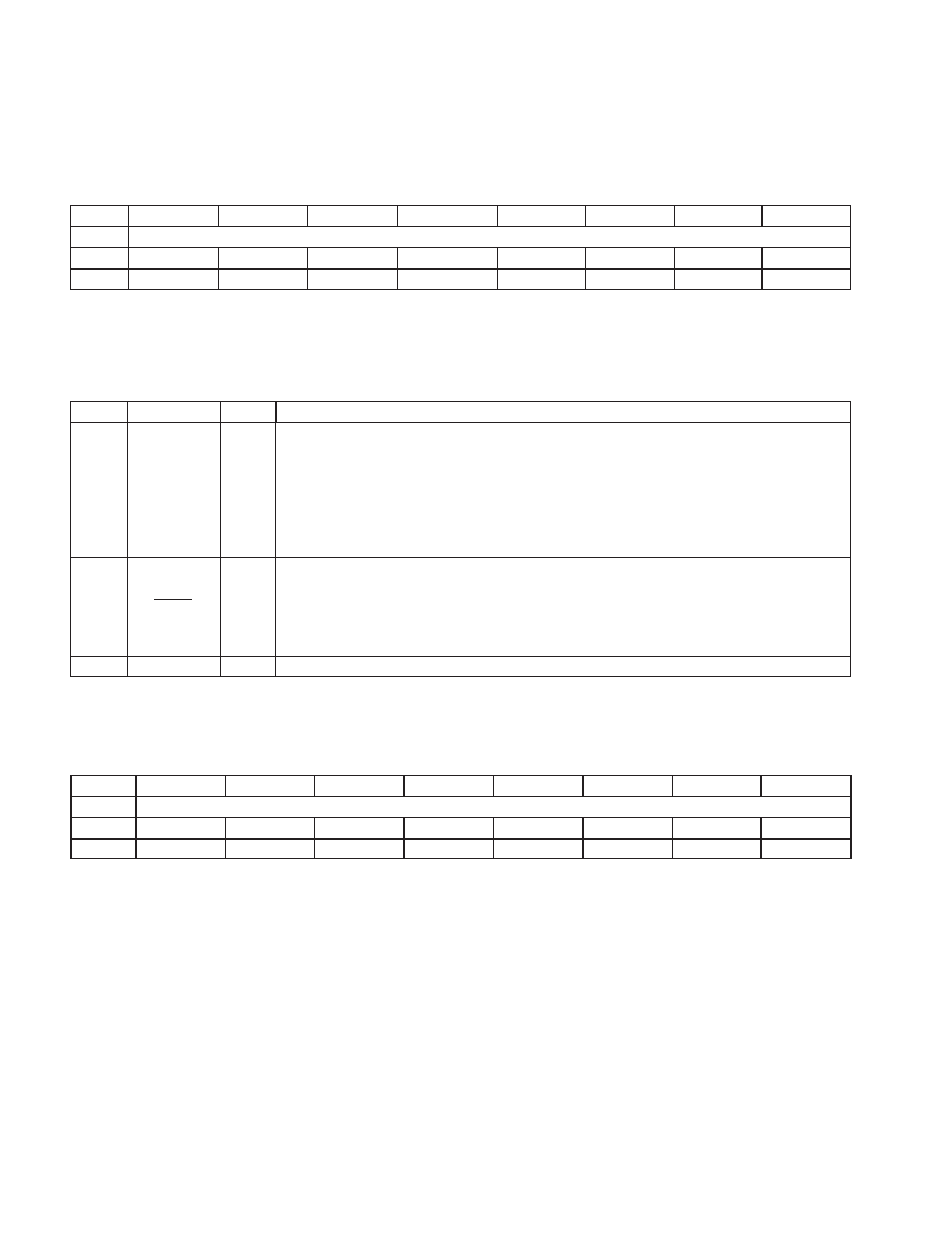

4.45 Power Management Control/Status Bridge Support Extensions Register

This register supports PCI bridge-specific functionality. It is required for all PCI-to-PCI bridges. See Table 4−21 for

a complete description of the register contents.

Bit

7

6

5

4

3

2

1

0

Name

Power management control/status bridge support extensions

Type

R

R

R

R

R

R

R

R

Default

1

1

0

0

0

0

0

0

Register:

Power management control/status bridge support extensions

Offset:

A6h (Functions 0, 1)

Type:

Read-only

Default: C0h

Table 4−21. Power Management Control/Status Bridge Support Extensions Register Description

BIT

SIGNAL

TYPE

FUNCTION

7

BPCC_EN

R

Bus power/clock control enable. This bit returns 1 when read. This bit is encoded as:

0 = Bus power/clock control is disabled.

1 = Bus power/clock control is enabled (default).

A 0 indicates that the bus power/clock control policies defined in the PCI Bus Power Management Interface

Specification are disabled. When the bus power/clock control enable mechanism is disabled, the power

state field (bits 1−0) of the power management control/status register (PCI offset A4h, see Section 4.44)

cannot be used by the system software to control the power or the clock of the secondary bus. A 1 indicates

that the bus power/clock control mechanism is enabled.

6

B2_B3

R

B2/B3 support for D3hot. The state of this bit determines the action that is to occur as a direct result of

programming the function to D3hot. This bit is only meaningful if bit 7 (BPCC_EN) is a 1. This bit is encoded

as:

0 = When the bridge is programmed to D3hot, its secondary bus has its power removed (B3).

1 = When the bridge function is programmed to D3hot, its secondary bus PCI clock is stopped (B2)

(default).

5−0

RSVD

R

Reserved. These bits return 0s when read.

4.46 Power-Management Data Register

The power-management data register returns 0s when read, because the CardBus functions do not report dynamic

data.

Bit

7

6

5

4

3

2

1

0

Name

Power-management data

Type

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

Register:

Power-management data

Offset:

A7h (functions 0, 1)

Type:

Read-only

Default:

00h