8 power manager scratch pad register (pspr), Power manager scratch pad register (pspr) -30, Pspr bit definitions -30 – Intel PXA255 User Manual

Page 92

3-30

Intel® PXA255 Processor Developer’s Manual

Clocks and Power Manager

3.5.8

Power Manager Scratch Pad Register (PSPR)

The PM contains a 32-bit register that can be used to save processor configuration information in

any desired format. The PSPR, shown in

, is a holding register that is powered during

sleep mode and is reset by hardware, watchdog, and GPIO resets. During run and turbo modes, any

value can be written to PSPR. The value can be read after sleep mode exits. The value in PSPR can

be used to represent the processor’s configuration before sleep mode is invoked.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

2

VFS

VDD Fault Status.

0 – nVDD_FAULT pin has not been asserted since it was last cleared by a reset or the

CPU.

1 – nVDD_FAULT pin was asserted in Run or idle mode and caused the chip to enter

sleep mode; bit is set only after wake up.

This bit is not set when nVDD_FAULT is asserted while in sleep mode.

Cleared by hardware, watchdog, and GPIO resets.

1

BFS

Battery Fault Status.

0 – nBATT_FAULT pin has not been asserted since it was last cleared by a reset or the

CPU.

1 – nBATT_FAULT pin has been asserted; bit is set only after wake up.

This bit can be set when nBATT_FAULT is asserted while in sleep mode.

Cleared by hardware, watchdog, and GPIO resets.

0

SSS

Software Sleep Status.

0 – Software has not entered sleep mode through the sleep mode bit since the SSS

was last cleared by a reset or the CPU.

1 – Chip was placed in sleep mode by setting the sleep mode bit.

Cleared by hardware, watchdog, and GPIO resets.

Table 3-13. PSSR Bit Definitions (Sheet 2 of 2)

0x40F0_0004

PSSR

Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

RD

H

PH

reser

ved

VF

S

BF

S

SS

S

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

Bits

Name

Description

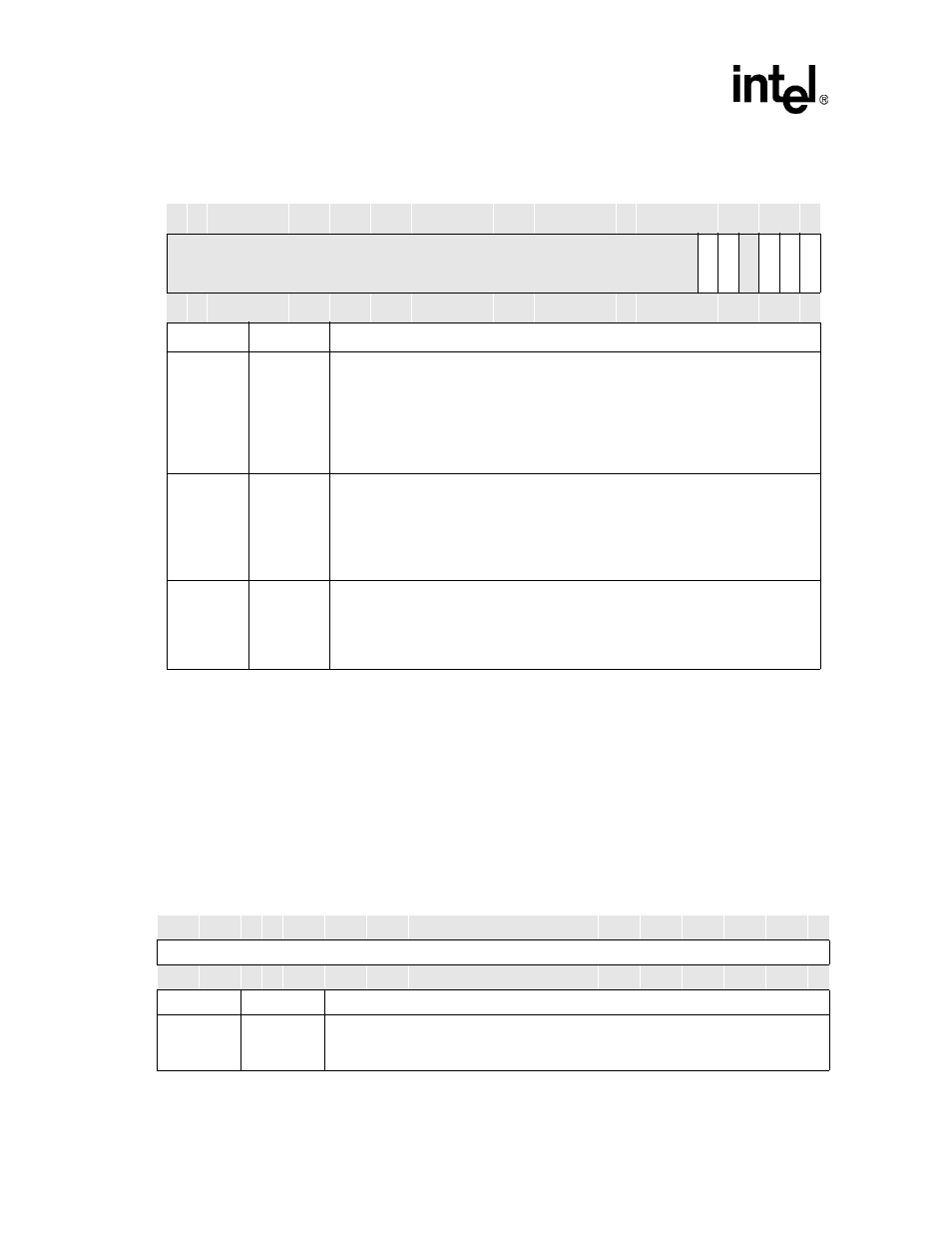

Table 3-14. PSPR Bit Definitions

0x40F0_0008

PSPR

Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

SP

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

[31:0]

SP

Scratch Pad

32-bit word is preserved in sleep mode.

Cleared by hardware, watchdog, and GPIO resets.