5 interrupt identification register (iir), Ier bit definitions -9 – Intel PXA255 User Manual

Page 365

Intel® PXA255 Processor Developer’s Manual

10-9

UARTs

Bit 7 of the IER is used to enable DMA requests. The IER also contains the unit enable and NRZ

coding enable control bits. Bits 7 through 4 are used differently from the standard 16550 register

definition.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

Note:

To ensure that the DMA controller and programmed I/O do not access the same FIFO, software

must not set the DMAE while the TIE or RAVIE bits are set to a 1.

10.4.2.5

Interrupt Identification Register (IIR)

The UART prioritizes interrupts in four levels (see

) and records them in the IIR. The

IIR, shown in

, stores information that indicates that a prioritized interrupt is pending

and identifies the source of the interrupt.

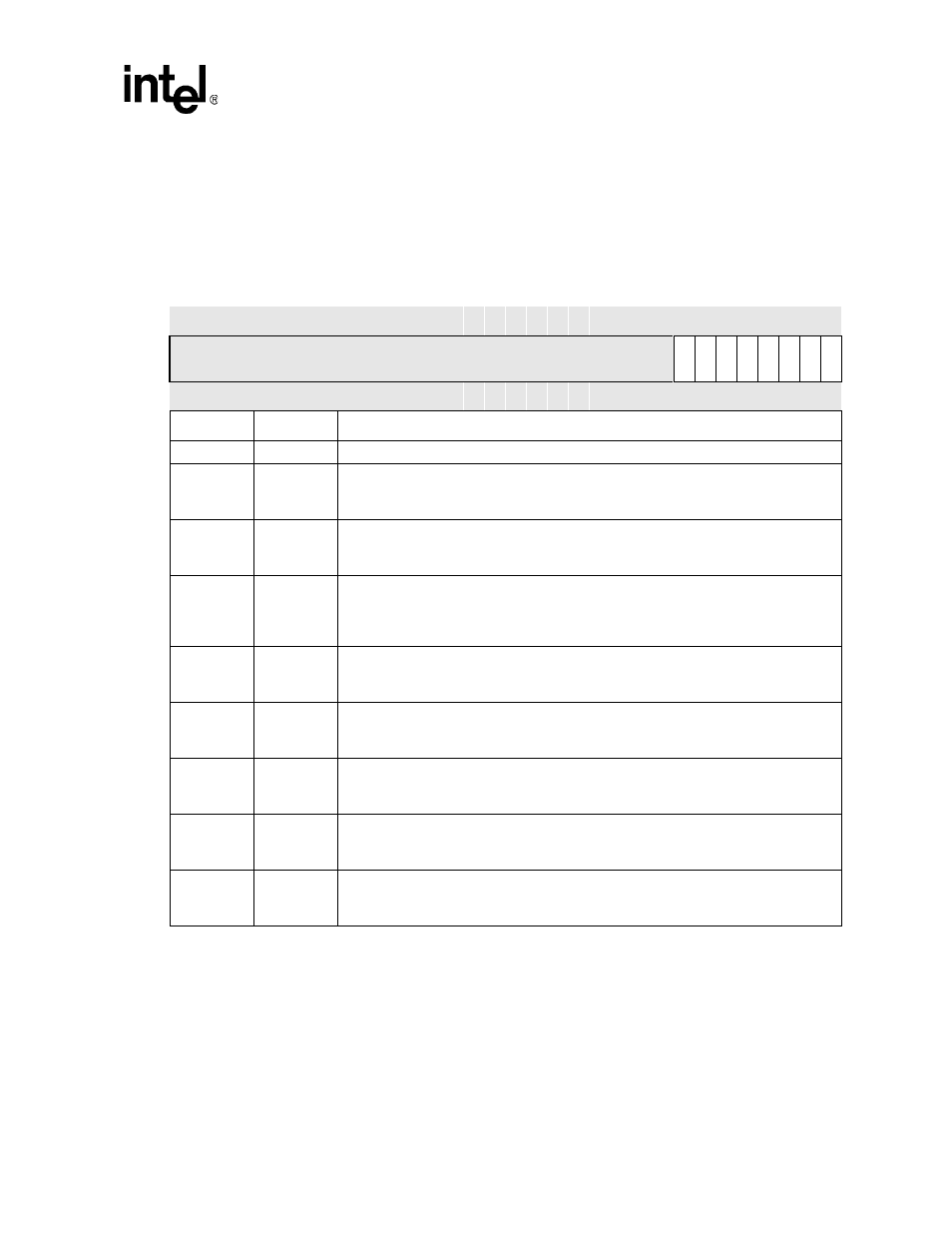

Table 10-7. IER Bit Definitions

Base+0x04 (DLAB=0)

Interrupt Enable Register

UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

DM

AE

UU

E

NR

Z

E

RT

O

IE

MI

E

RL

SE

TIE

RA

VI

E

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:8

—

reserved

7

DMAE

DMA Requests Enable.

0 – DMA requests are disabled

1 – DMA requests are enabled

6

UUE

UART Unit Enable.

0 – The unit is disabled

1 – The unit is enabled

5

NRZE

NRZ coding Enable. NRZ encoding/decoding is only used in UART mode, not in infrared

mode. If the slow infrared receiver or transmitter is enabled, NRZ coding is disabled.

0 – NRZ coding disabled

1 – NRZ coding enabled

4

RTOIE

Character Timeout Indication Interrupt Enable.

0 – Character Timeout Indication interrupt disabled

1 – Character Timeout Indication interrupt enabled

3

MIE

Modem Interrupt Enable.

0 – Modem Status interrupt disabled

1 – Modem Status interrupt enabled

2

RLSE

Receiver Line Status Interrupt Enable.

0 – Receiver Line Status interrupt disabled

1 – Receiver Line Status interrupt enabled

1

TIE

Transmit Data request Interrupt Enable.

0 – Transmit FIFO Data Request interrupt disabled

1 – Transmit FIFO Data Request interrupt enabled

0

RAVIE

Receiver Data Available Interrupt Enable.

0 – Receiver Data Available (Trigger level reached) interrupt disabled

1 – Receiver Data Available (Trigger level reached) interrupt enabled