4 dma enable (dme), 5 bits 5:4 reserved, 6 receive fifo not empty (rne) – Intel PXA255 User Manual

Page 434: 7 receive short packet (rsp), Udccs5/10/15 bit definitions -34

12-34

Intel® PXA255 Processor Developer’s Manual

USB Device Controller

12.6.7.4

DMA Enable (DME)

The DMA enable is used by the UDC to control the timing of the data received interrupt. If the bit

is set, the interrupt is asserted when the end of packet is received and the receive FIFO has less than

32 bytes of data in it. If the bit is not set, the interrupt is asserted when the end of packet is received

and all of the received data is still in the receive FIFO.

12.6.7.5

Bits 5:4 Reserved

Bits 5:4 are reserved for future use.

12.6.7.6

Receive FIFO Not Empty (RNE)

The receive FIFO not empty bit indicates that the receive FIFO has unread data in it. When the

UDCCSx[RPC] bit is set, this bit must be read to determine if there is any data in the FIFO that

DMA did not read. The receive FIFO must continue to be read until this bit clears or data will be

lost.

12.6.7.7

Receive Short Packet (RSP)

The receive short packet bit is used by the UDC to indicate that the received OUT packet in the

active buffer currently being read is a short packet or zero-sized packet. This bit is updated by the

UDC after the last byte is read from the active buffer and reflects the status of the new active

buffer. If UDCCSx[RSP] is a one and UDCCSx[RNE] is a zero, it indicates a zero-length packet. If

a zero-length packet is present, the core must not read the data register. UDCCSx[RSP] clears

when the next OUT packet is received.

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

12.6.8

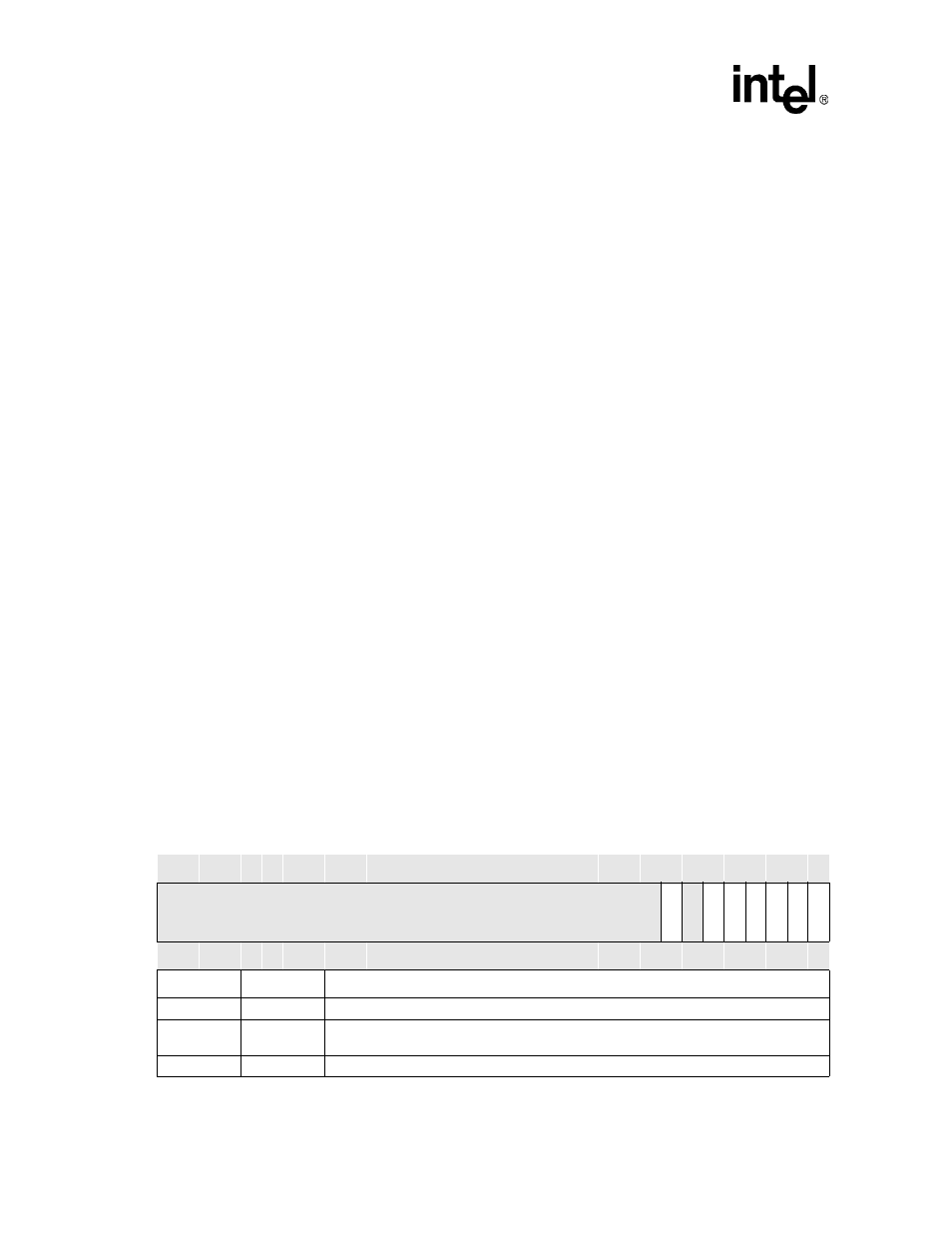

UDC Endpoint x Control/Status Register (UDCCS5/10/15)

UDCCS5/10/15, shown in

contains 6 bits that are used to operate endpoint(x), an

Interrupt IN endpoint.

Table 12-19. UDCCS5/10/15 Bit Definitions (Sheet 1 of 2)

0x 4060_0024

0x 4060_0038

0x 4060_004C

UDCCS5

UDCCS5

UDCCS15

USB Device Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

TS

P

reser

ved

FS

T

SS

T

TU

R

FTF

TP

C

TF

S

Reset

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

0

0

0

0

0

1

Bits

Name

Description

31:8

—

reserved

7

TSP

Transmit short packet (read/write 1 to set).

1 = Short packet ready for transmission.

6

—

reserved